www.ti.com

CONTROL_MODULE Registers

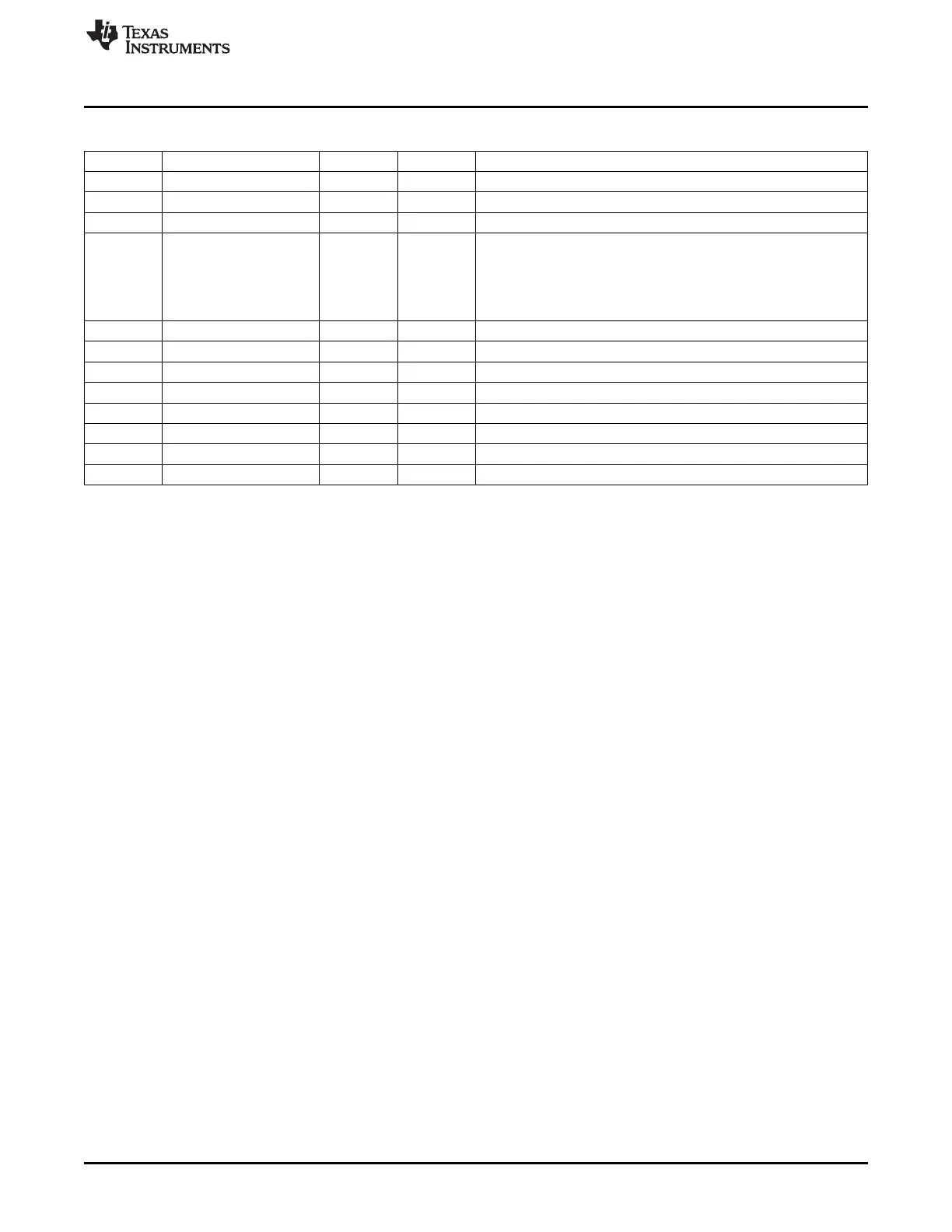

Table 9-86. dpll_pwr_sw_ctrl Register Field Descriptions (continued)

Bit Field Type Reset Description

18 iso_disp R/W 0h Drives ISO of DISP DPLL.

17 pgoodin_disp R/W 1h Drives PGOODIN of DISP DPLL.

16 ponin_disp R/W 1h Drives PONIN of DISP DPLL.

15 sw_ctrl_per_dpll R/W 0h

Enable software control over PER DPLL RET, RESET, ISO,

PGOODIN, PONIN for power savings.

0: PRCM controls the DPLL reset, RET = 0, ISO = 0, PGOODIN = 1,

PONIN = 1.

1: Controlled by corresponding bits in this register.

14 Reserved R 0h

13 isoscan_per R/W 0h Drives ISOSCAN of PER PLL.

12 ret_per R/W 0h Drives RET of PER DPLL.

11 reset_per R/W 0h Drives RESET signal of PER DPLL.

10 iso_per R/W 0h Drives ISO signal of PER DPLL.

9 pgoodin_per R/W 1h Drives PGOODIN signal of PER DPLL.

8 ponin_per R/W 1h Drives PONIN signal of PER DPLL.

7-0 Reserved R 0h

841

SPRUH73H–October 2011–Revised April 2013 Control Module

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...