www.ti.com

DMTimer

20.1.5.16 TSICR Register (offset = 54h) [reset = 0h]

TSICR is shown in Figure 20-24 and described in Table 20-26.

Access to this register is not stalled even if the timer is in non-posted mode configuration. To abort any

wrong behavior, software can permanently reset the functional part of the module. Also in case of a wrong

hardware PIFREQRATIO tied the POSTED field can be reprogrammed on the fly, so deadlock situation

cannot happen. Reset value of POSTED depends on hardware integration module at design time.

Software must read POSTED field to get the hardware module configuration.

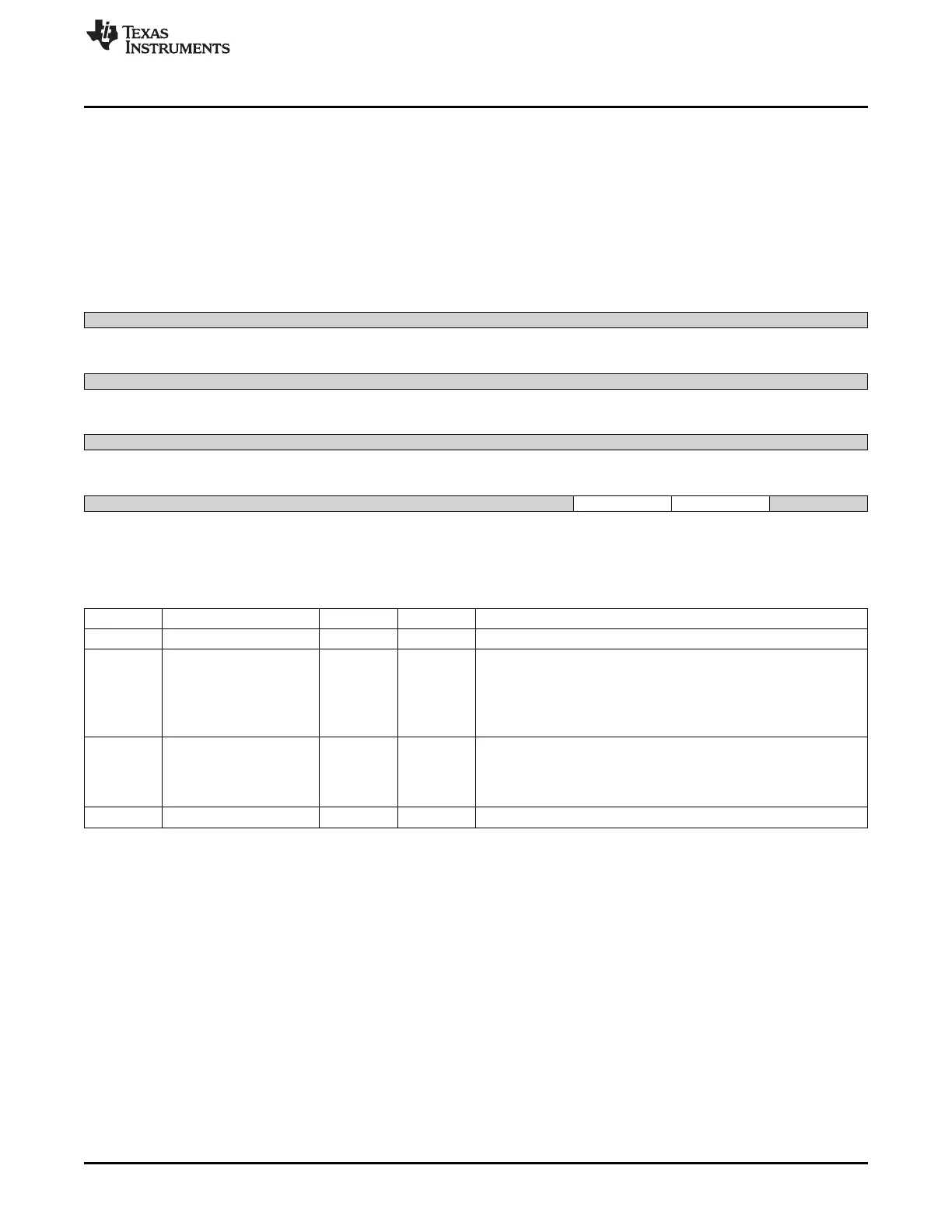

Figure 20-24. TSICR Register

31 30 29 28 27 26 25 24

Reserved

R-0h

23 22 21 20 19 18 17 16

Reserved

R-0h

15 14 13 12 11 10 9 8

Reserved

R-0h

7 6 5 4 3 2 1 0

Reserved POSTED SFT Reserved

R-0h R/W-0h R/W-0h R-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

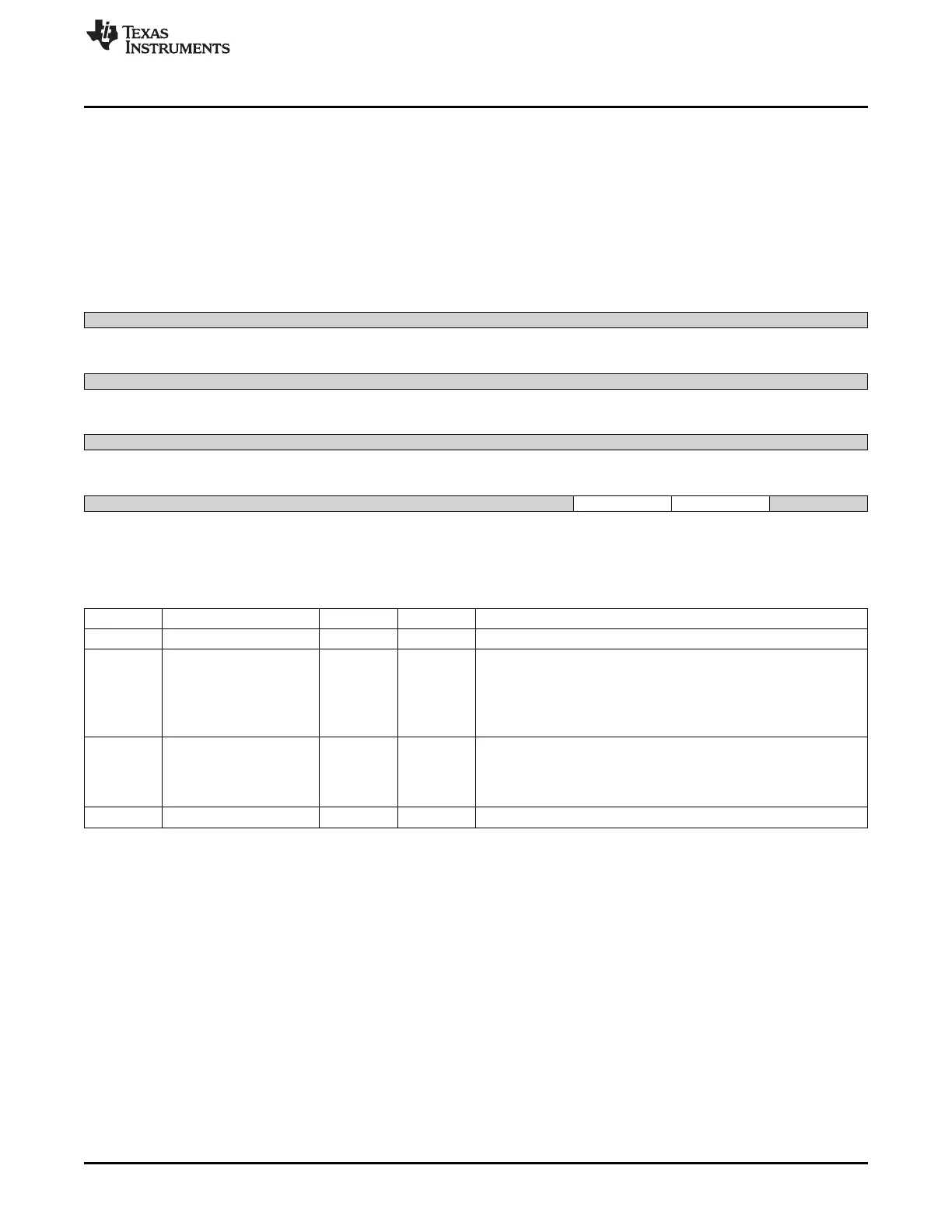

Table 20-26. TSICR Register Field Descriptions

Bit Field Type Reset Description

31-3 Reserved R 0h

2 POSTED R/W 0h

PIFREQRATIO

0x0 = Posted mode inactive: will delay the command accept output

signal. NOTE: This setting is not recommended on this device.

0x1 = Posted mode active (clocks ratio needs to fit freq (timer) less

than freq (OCP)/4 frequency requirement)

1 SFT R/W 0h This bit resets all the function parts of the module.

During reads it always returns 0.

0x0 = Software reset is enabled

0x1 = Software reset is disabled

0 Reserved R 0h

3583

SPRUH73H–October 2011–Revised April 2013 Timers

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...