www.ti.com

UART Registers

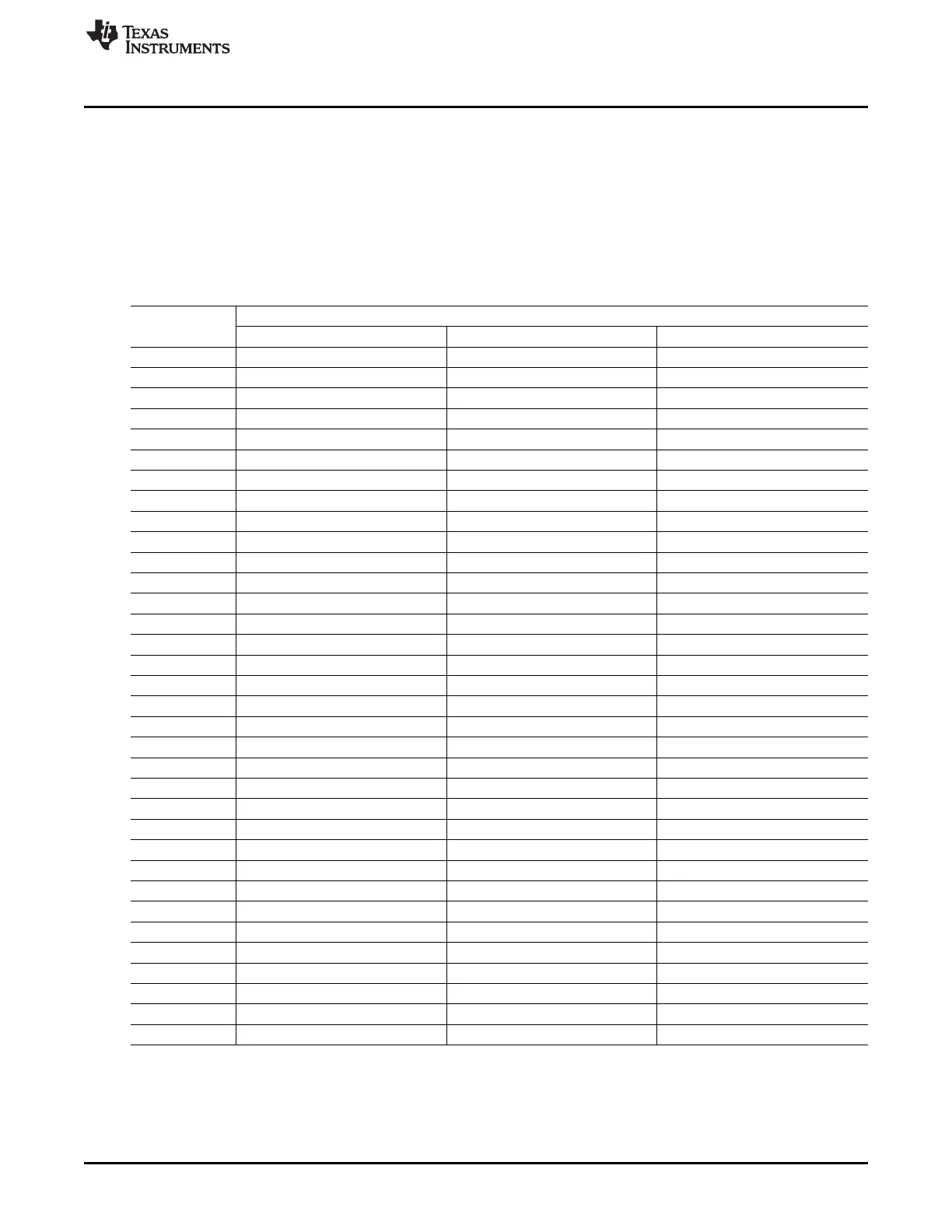

19.5 UART Registers

19.5.1 UART Registers

Each register is selected using a combination of address and, for some, LCR register bit settings as

shown in Table 19-29. The following registers are accessible by the local host (LH) at address = module

base address + address offset. The module base address is the module start address. Note that register

address offsets depends upon the module address alignment at the system top level.

Table 19-29. UART Registers

Registers

Address Offset LCR[7] = 0 LCR[7:0] ≠ BFh LCR[7:0] = BFh

Read Write Read Write Read Write

0h RHR THR DLL DLL DLL DLL

4h IER

(1)

IER

(1)

DLH DLH DLH DLH

8h IIR FCR

(2)

IIR FCR

(2)

EFR EFR

Ch LCR LCR LCR LCR LCR LCR

10h MCR

(2)

MCR

(2)

MCR

(2)

MCR

(2)

XON1/ADDR1 XON1/ADDR1

14h LSR - LSR - XON2/ADDR2 XON2/ADDR2

18h MSR/TCR

(3)

TCR

(3)

MSR/TCR

(3)

TCR

(3)

XOFF1/TCR

(3)

XOFF1/TCR

(3)

1Ch SPR/TLR

(3)

SPR/TLR

(3)

SPR/TLR

(3)

SPR/TLR

(3)

XOFF2/TLR

(3)

XOFF2/TLR

(3)

20h MDR1 MDR1 MDR1 MDR1 MDR1 MDR1

24h MDR2 MDR2 MDR2 MDR2 MDR2 MDR2

28h SFLSR TXFLL SFLSR TXFLL SFLSR TXFLL

2Ch RESUME TXFLH RESUME TXFLH RESUME TXFLH

30h SFREGL RXFLL SFREGL RXFLL SFREGL RXFLL

34h SFREGH RXFLH SFREGH RXFLH SFREGH RXFLH

38h BLR BLR UASR - UASR -

3Ch ACREG ACREG - - - -

40h SCR SCR SCR SCR SCR SCR

44h SSR SSR[2] SSR SSR[2] SSR SSR[2]

48h EBLR EBLR - - - -

50h MVR - MVR - MVR -

54h SYSC SYSC SYSC SYSC SYSC SYSC

58h SYSS - SYSS - SYSS -

5Ch WER WER WER WER WER WER

60h CFPS CFPS CFPS CFPS CFPS CFPS

64h RXFIFO_LVL RXFIFO_LVL RXFIFO_LVL RXFIFO_LVL RXFIFO_LVL RXFIFO_LVL

68h TXFIFO_LVL TXFIFO_LVL TXFIFO_LVL TXFIFO_LVL TXFIFO_LVL TXFIFO_LVL

6Ch IER2 IER2 IER2 IER2 IER2 IER2

70h ISR2 ISR2 ISR2 ISR2 ISR2 ISR2

74h FREQ_SEL FREQ_SEL FREQ_SEL FREQ_SEL FREQ_SEL FREQ_SEL

78h - - - - - -

7Ch - - - - - -

80h MDR3 MDR3 MDR3 MDR3 MDR3 MDR3

84h TXDMA TXDMA TXDMA TXDMA TXDMA TXDMA

(1)

In UART modes, IER[7:4] can only be written when EFR[4] = 1; in IrDA/CIR modes, EFR[4] has no impact on the access to

IER[7:4].

(2)

MCR[7:5] and FCR[5:4] can only be written when EFR[4] = 1.

(3)

Transmission control register (TCR) and trigger level register (TLR) are accessible only when EFR[4] = 1 and MCR[6] = 1.

3505

SPRUH73H–October 2011–Revised April 2013 Universal Asynchronous Receiver/Transmitter (UART)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...