www.ti.com

McASP Registers

22.4.1.12 Digital Mode Control Register (DITCTL)

The DIT mode control register (DITCTL) controls DIT operations of the McASP. The DITCTL is shown in

Figure 22-50 and described in Table 22-23.

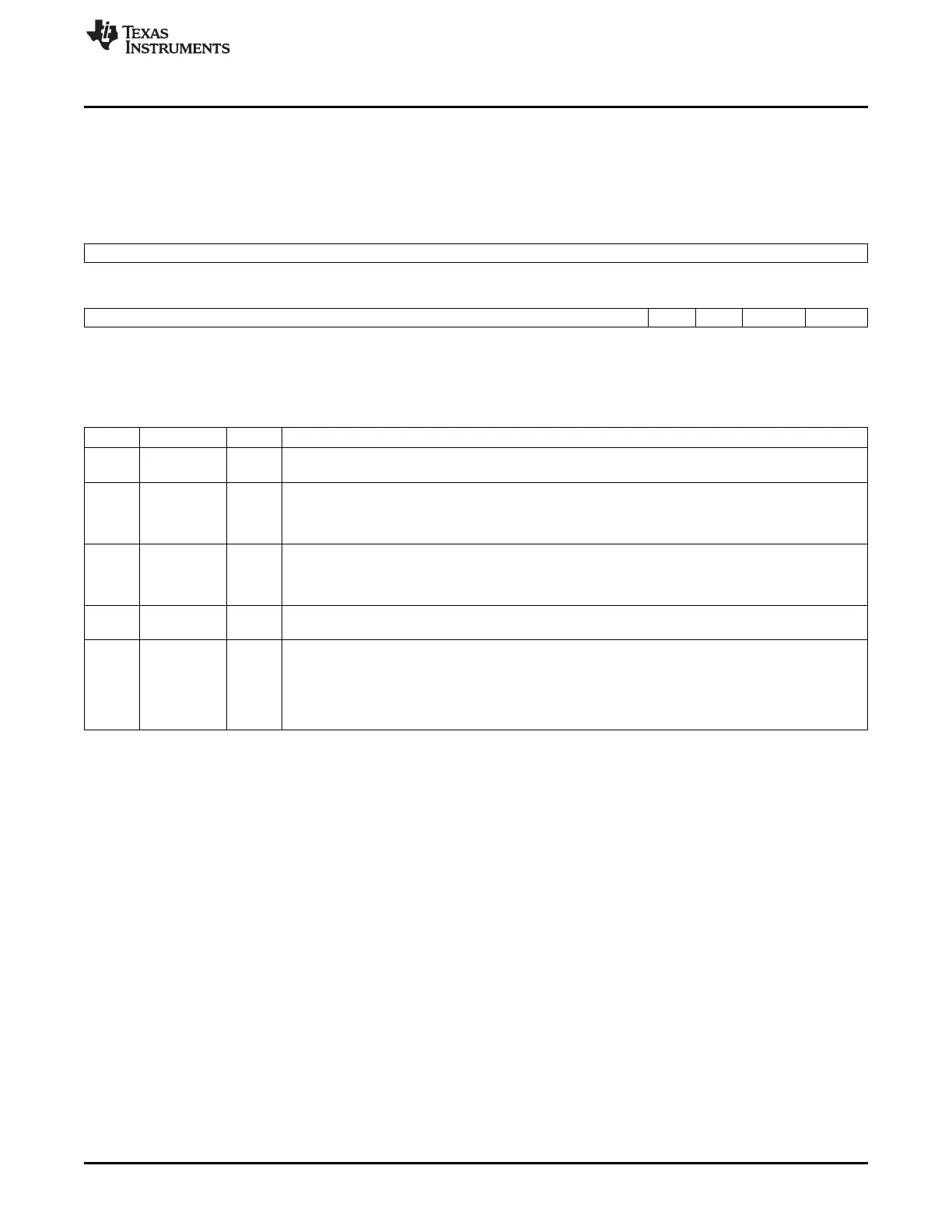

Figure 22-50. Digital Mode Control Register (DITCTL)

31 16

Reserved

R-0

15 4 3 2 1 0

Reserved VB VA Rsvd DITEN

R-0 R/W-0 R/W-0 R-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

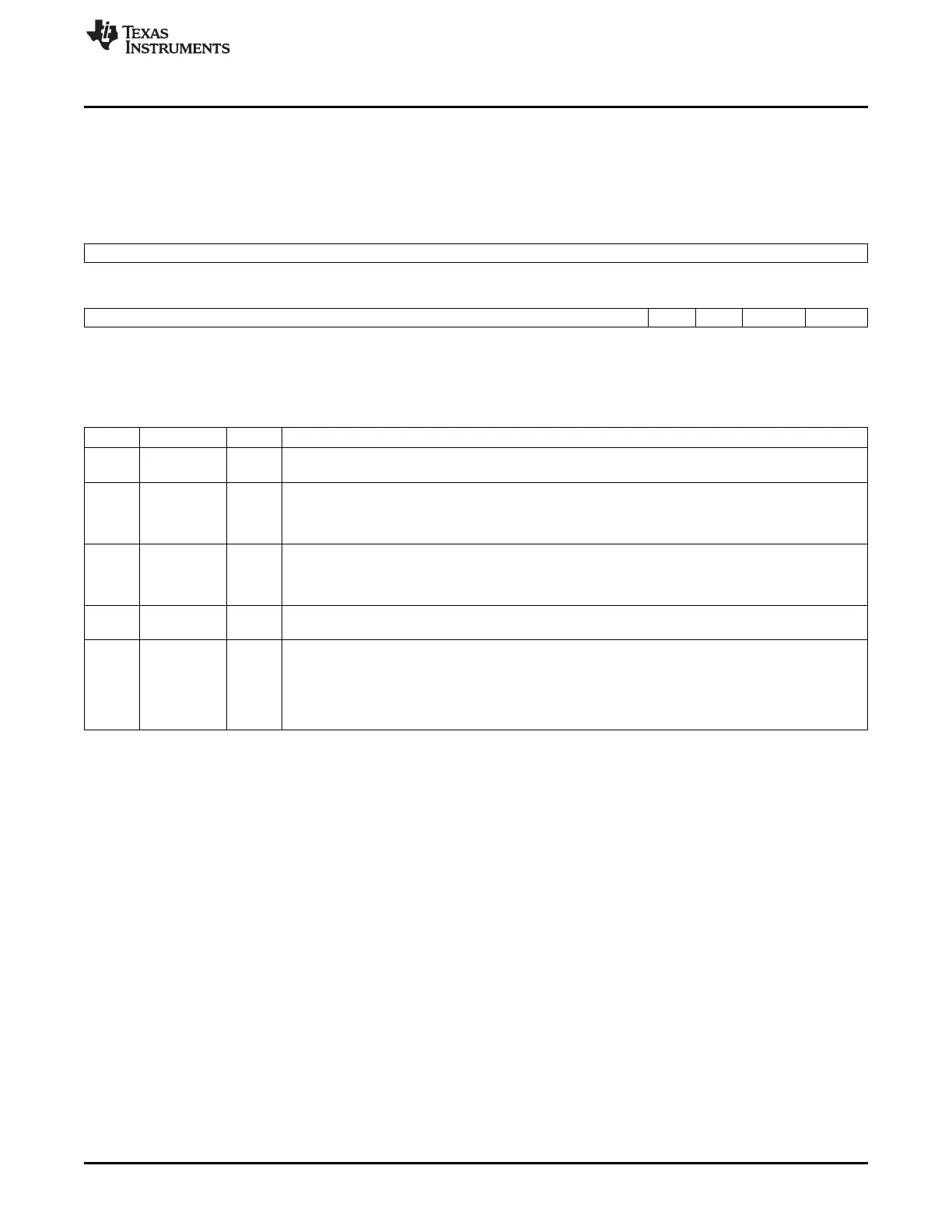

Table 22-23. Digital Mode Control Register (DITCTL) Field Descriptions

Bit Field Value Description

31-4 Reserved 0 Reserved. The reserved bit location always returns the default value. A value written to this field has no

effect. If writing to this field, always write the default value for future device compatibility.

3 VB Valid bit for odd time slots (DIT right subframe).

0 V bit is 0 during odd DIT subframes.

1 V bit is 1 during odd DIT subframes.

2 VA Valid bit for even time slots (DIT left subframe).

0 V bit is 0 during even DIT subframes.

1 V bit is 1 during even DIT subframes.

1 Reserved 0 Reserved. The reserved bit location always returns the default value. A value written to this field has no

effect. If writing to this field, always write the default value for future device compatibility.

0 DITEN DIT mode enable bit. DITEN should only be changed while the XSMRST bit in GBLCTL is in reset (and

for startup, XSRCLR also in reset). However, it is not necessary to reset the XCLKRST or XHCLKRST

bits in GBLCTL to change DITEN.

0 DIT mode is disabled. Transmitter operates in TDM or burst mode.

1 DIT mode is enabled. Transmitter operates in DIT encoded mode.

3847

SPRUH73H–October 2011–Revised April 2013 Multichannel Audio Serial Port (McASP)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...