Functional Description

www.ti.com

• SIR mode: Divisor value = Operating frequency/(16x baud rate)

• MIR mode: Divisor value = Operating frequency/(41x/42x baud rate)

• FIR mode: Divisor value = None

Table 19-28 lists the IrDA baud rate settings.

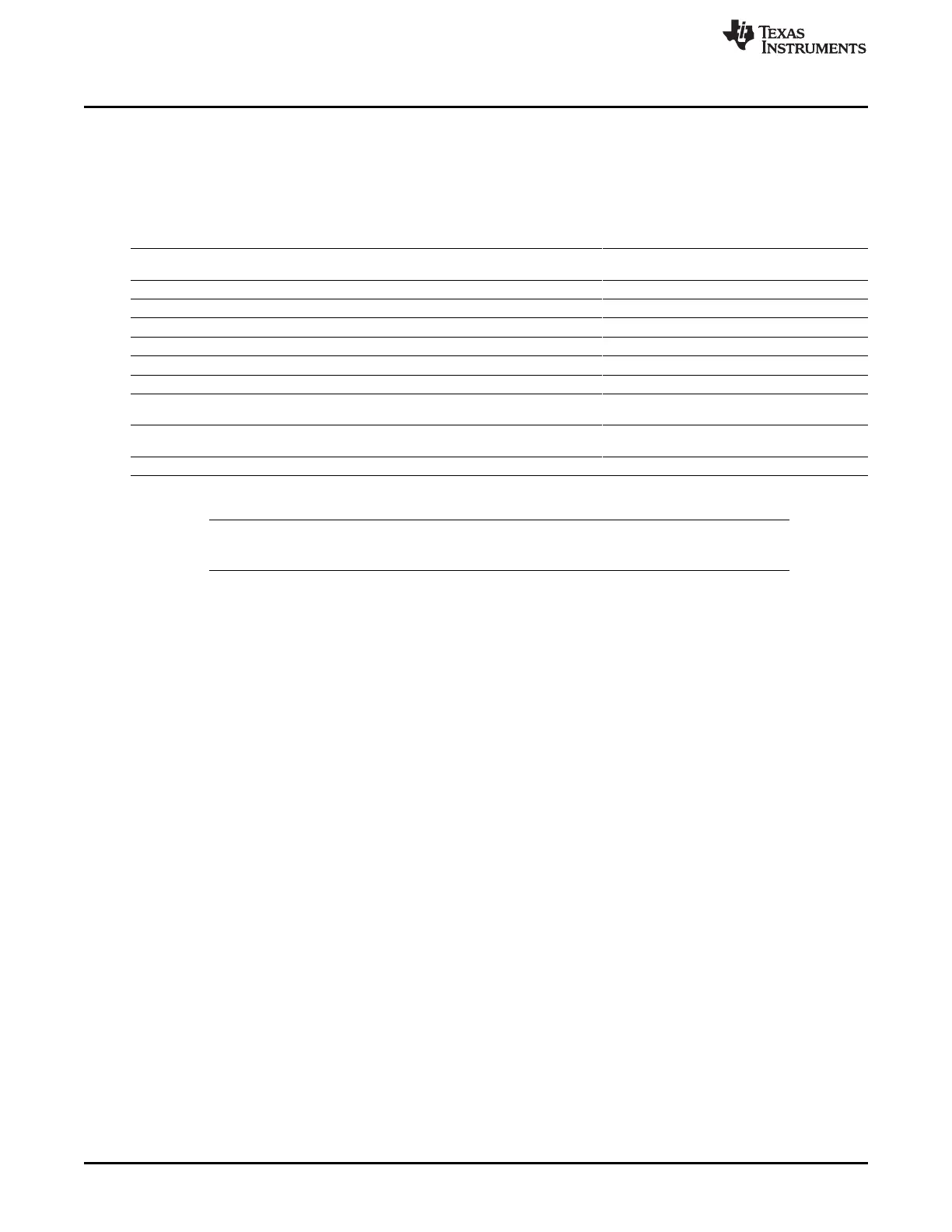

Table 19-28. IrDA Baud Rate Settings

Baud Rate IR Mode Baud Multiple Encoding DLH, DLL Actual Baud Error (%) Source Jitter Pulse Duration

(Decimal) Rate (%)

2.4 kbps SIR 16x 3/16 1250 2.4 kbps 0 0 78.1 µs

9.6 kbps SIR 16x 3/16 312 9.6153 kbps +0.16 0 19.5 µs

19.2 kbps SIR 16x 3/16 156 19.231 kbps +0.16 0 9.75 µs

38.4 kbps SIR 16x 3/16 78 38.462 kbps +0.16 0 4.87 µs

57.6 kbps SIR 16x 3/16 52 57.692 kbps +0.16 0 3.25 µs

115.2 kbps SIR 16x 3/16 26 115.38 kbps +0.16 0 1.62 µs

0.576 MIR 41x/42x 1/4 2 0.5756 Mbps

(1)

0 +1.63/–0.80 416 ns

Mbps

1.152 MIR 41x/42x 1/4 1 1.1511 Mbps

(1)

0 +1.63/–0.80 208 ns

Mbps

4 Mbps FIR 6x 4 PPM – 4 Mbps 0 0 125 ns

(1)

Average value

NOTE: Baud rate error and source jitter table values do not include 48-MHz reference clock error

and jitter.

19.3.8.2.6 IrDA Data Formatting

The methods described in this section apply to all IrDA modes (SIR, MIR, and FIR).

19.3.8.2.6.1 IR RX Polarity Control

The UARTi.UART_MDR2[6] IRRXINVERT bit provides the flexibility to invert the uarti_rx_irrx pin in the

UART to ensure that the protocol at the output of the transceiver has the same polarity at module level. By

default, the uarti_rx_irrx pin is inverted because most transceivers invert the IR receive pin.

19.3.8.2.6.2 IrDA Reception Control

The module can transmit and receive data, but when the device is transmitting, the IR RX circuitry is

automatically disabled by hardware.

Operation of the uarti_rx_irrx input can be disabled by the UARTi.UART_ACREG[5] DIS_IR_RX bit.

19.3.8.2.6.3 IR Address Checking

In all IR modes, when address checking is enabled, only frames intended for the device are written to the

RX FIFO. This restriction avoids receiving frames not meant for this device in a multipoint infrared

environment. It is possible to program two frame addresses that the UART IrDA receives, with the

UARTi.UART_XON1_ADDR1[7:0] XON_WORD1 and UARTi.UART_XON2_ADDR2[7:0] XON_WORD2 bit

fields.

Setting the UART_EFR[0] bit to 1 selects address1 checking. Setting the UART_EFR[1] bit to 1 selects

address2 checking. Setting the UART_EFR[1:0] bit field to 0 disables all address checking operations. If

both bits are set, the incoming frame is checked for private and public addresses.

If address checking is disabled, all received frames write to the RX FIFO.

19.3.8.2.6.4 Frame Closing

A transmission frame can be terminated in two ways:

3486

Universal Asynchronous Receiver/Transmitter (UART) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...