CONTROL_MODULE Registers

www.ti.com

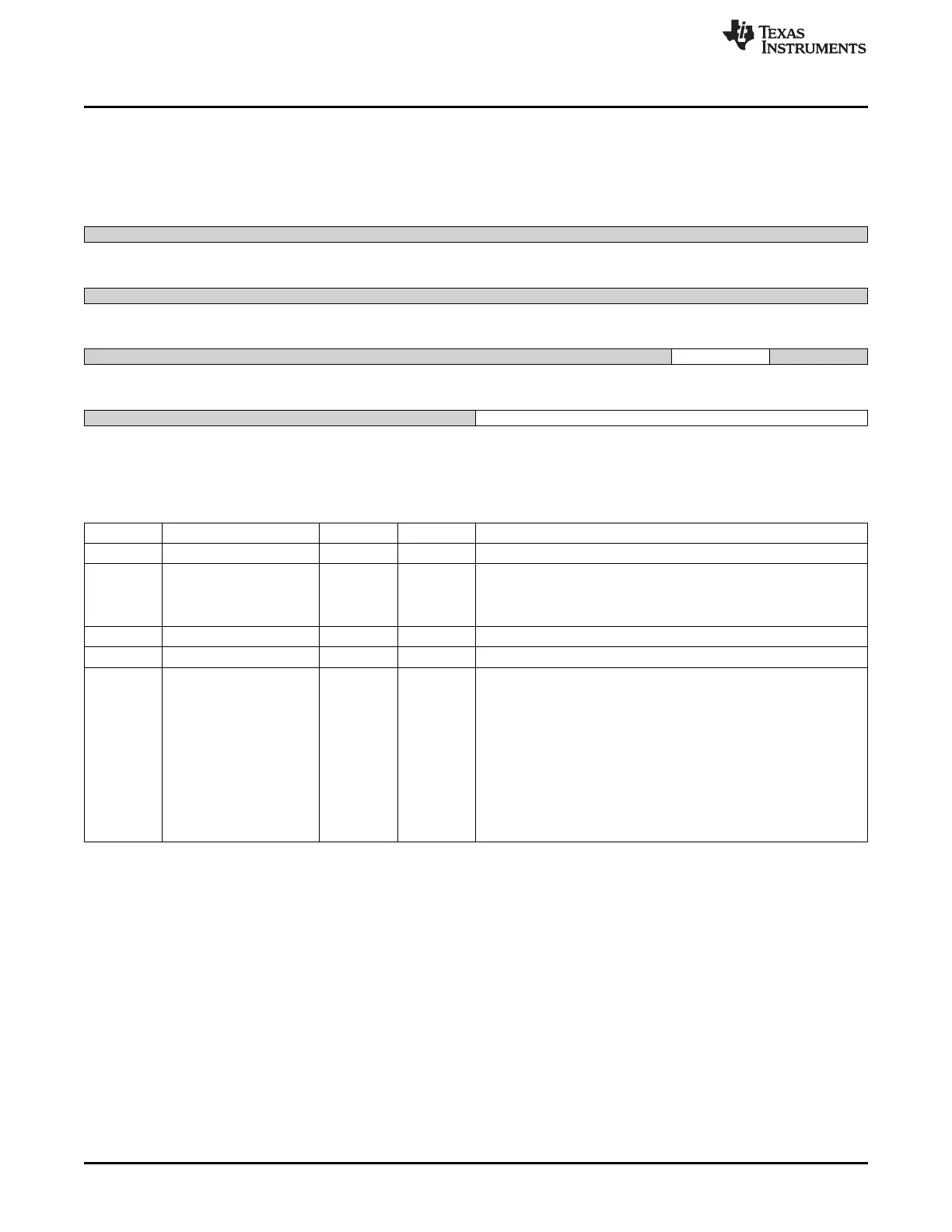

9.3.40 mpuss_hw_debug_sel Register (offset = 6A4h) [reset = 0h]

mpuss_hw_debug_sel is shown in Figure 9-43 and described in Table 9-50.

Figure 9-43. mpuss_hw_debug_sel Register

31 30 29 28 27 26 25 24

Reserved

R-0h

23 22 21 20 19 18 17 16

Reserved

R-0h

15 14 13 12 11 10 9 8

Reserved hw_dbg_gate_en Reserved

R-0h R/W-0h R-0h

7 6 5 4 3 2 1 0

Reserved hw_dbg_sel

R-0h R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

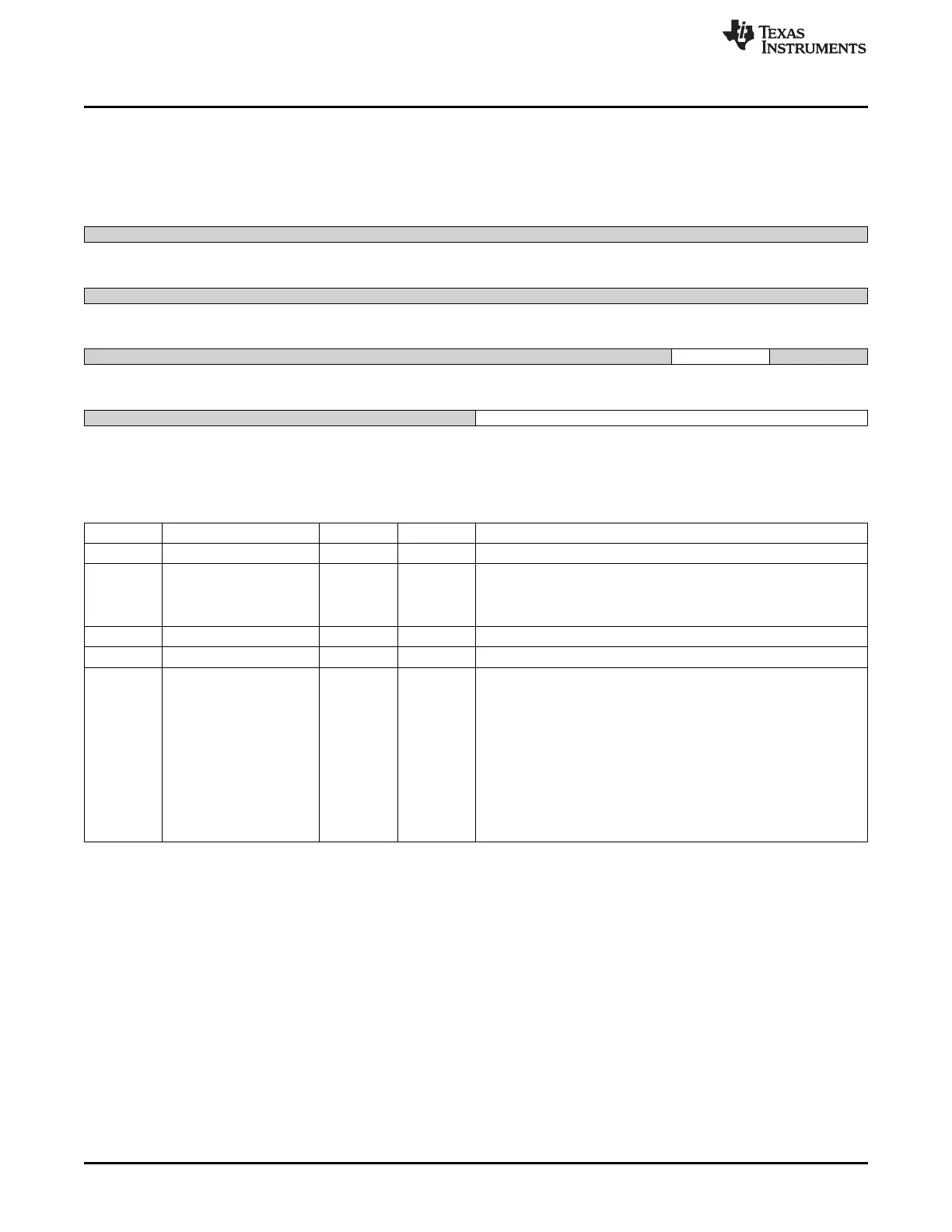

Table 9-50. mpuss_hw_debug_sel Register Field Descriptions

Bit Field Type Reset Description

31-10 Reserved R 0h

9 hw_dbg_gate_en R/W 0h To save power input to MPUSS_HW_DBG_INFO is gated off to all

zeros when HW_DBG_GATE_EN bit is low.

0: Debug info gated off

1: Debug info not gated off

8 Reserved R 0h

7-4 Reserved R 0h

3-0 hw_dbg_sel R/W 0h Selects which Group of signals are sent out to the

MODENA_HW_DBG_INFO register. Please see MPU functional

spec for more details

0000: Group 0

0001: Group 1

0010: Group 2

0011: Group 3

0100: Group 4

0101: Group 5

0110: Group 6

0111: Group 7

1xxx: Reserved

804

Control Module SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...