www.ti.com

EMIF

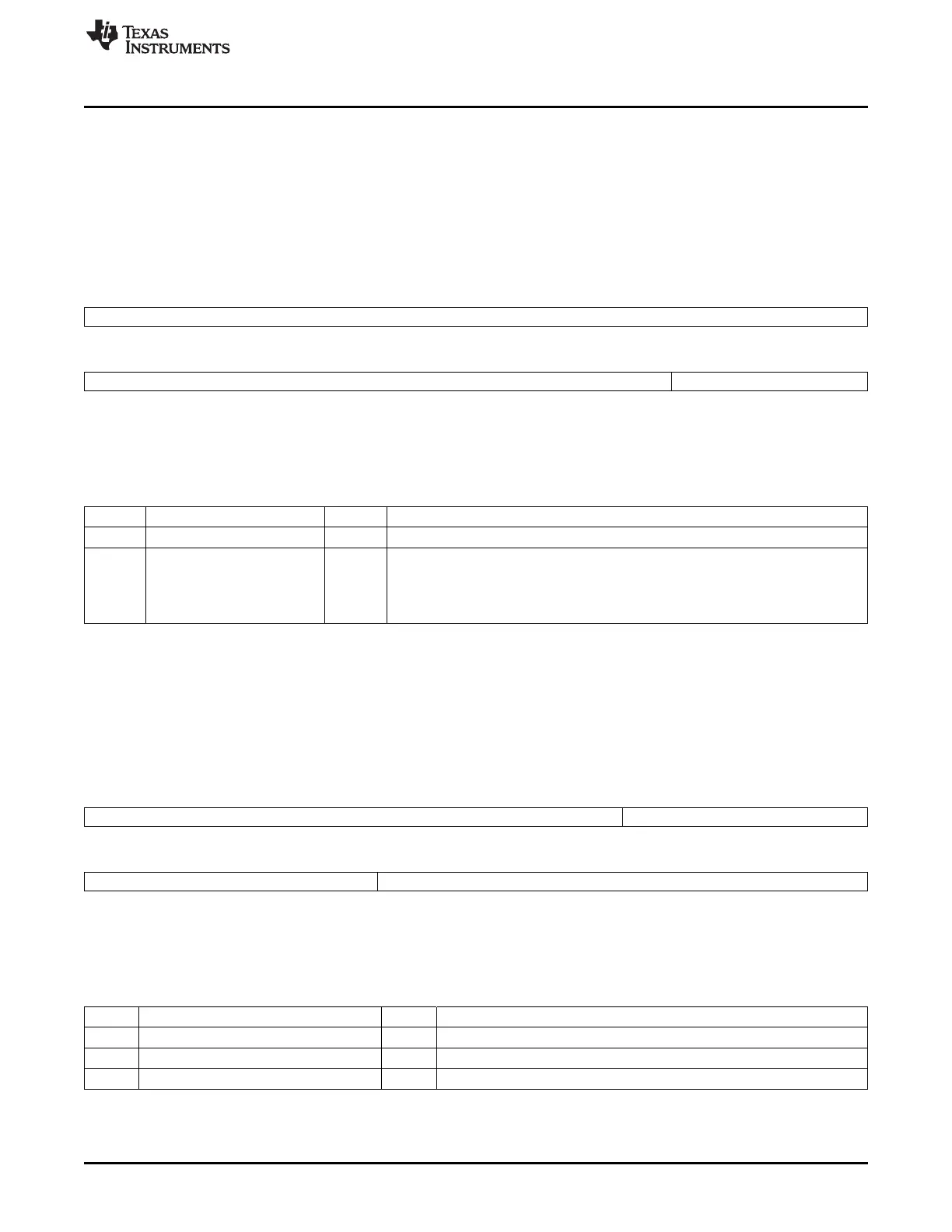

7.3.6.9 DDR PHY Data Macro 0/1 DQS Gate Training Init Mode Ratio Selection Register

(DATA0/1_REG_PHY_GATELVL_INIT_MODE_0)

The DDR PHY Data Macro 0/1 DQS Gate Training Init Mode Ratio Selection

Register(DATA0/1_REG_PHY_GATELVL_INIT_MODE_0) is shown in the figure and table below.

Figure 7-136. DDR PHY Data Macro 0/1 DQS Gate Training Init Mode Ratio Selection Register

(DATA0/1_REG_PHY_GATELVL_INIT_MODE_0)

31 16

Reserved

R-0

15 1 0

Reserved GATELVL _INIT _MODE_SEL

R-0 W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 7-159. DDR PHY Data Macro 0/1 DQS Gate Training Init Mode Ratio Selection Register

(DATA0/1_REG_PHY_GATELVL_INIT_MODE_0) Field Descriptions

Bit Field Value Description

31-1 Reserved 0 Reserved

0 GATELVL_INIT_MODE_SEL User programmable init ratio selection mode for DQS Gate Training FSM.

0 Selects a starting ratio value based on Write Leveling of the same data slice.

1 selects a starting ratio value based on

DATA0/1_REG_PHY_GATELVL_INIT_RATIO_0 value programmed by the user.

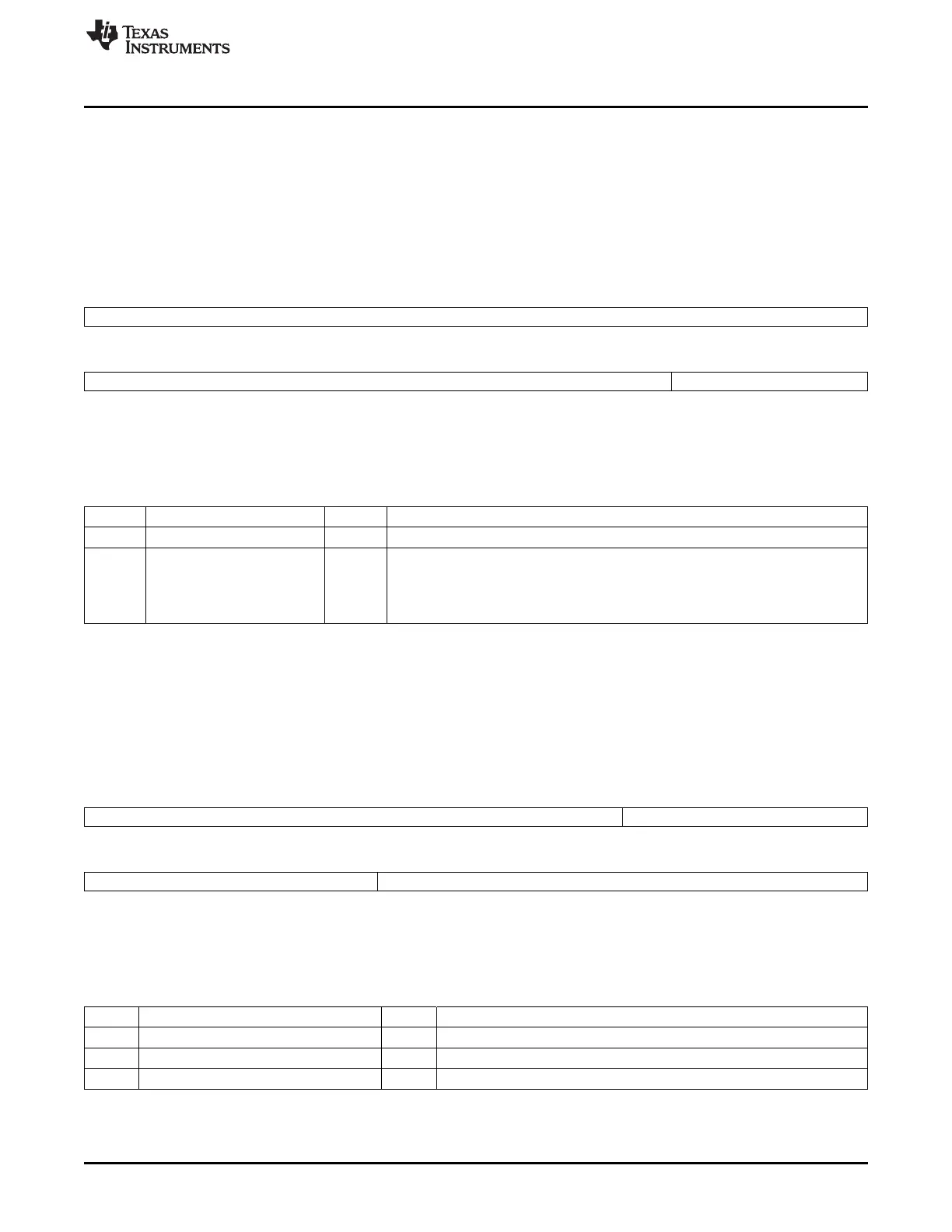

7.3.6.10 DDR PHY Data Macro 0/1 DQS Gate Slave Ratio Register

(DATA0/1_REG_PHY_FIFO_WE_SLAVE_RATIO_0)

The DDR PHY Data Macro 0/1 DQS Gate Slave Ratio Register

(DATA0/1_REG_PHY_FIFO_WE_SLAVE_RATIO_0) is shown in the figure and table below.

Figure 7-137. DDR PHY Data Macro 0/1 DQS Gate Slave Ratio

Register(DATA0/1_REG_PHY_FIFO_WE_SLAVE_RATIO_0)

31 20 19 16

Reserved Reserved

R-0 R-0

15 10 9 0

Reserved FIFO_WE_SLAVE_RATIO_CS0

R-0 W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 7-160. DDR PHY Data Macro 0/1 DQS Gate Slave Ratio Register

(DATA0/1_REG_PHY_FIFO_WE_SLAVE_RATIO_0) Field Descriptions

Bit Field Value Description

31-20 Reserved 0 Reserved

19-10 Reserved 0h Reserved

9-0 RD_DQS_GATE _SLAVE_RATIO_CS0 0h Ratio value for fifo we for CS0.

473

SPRUH73H–October 2011–Revised April 2013 Memory Subsystem

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...