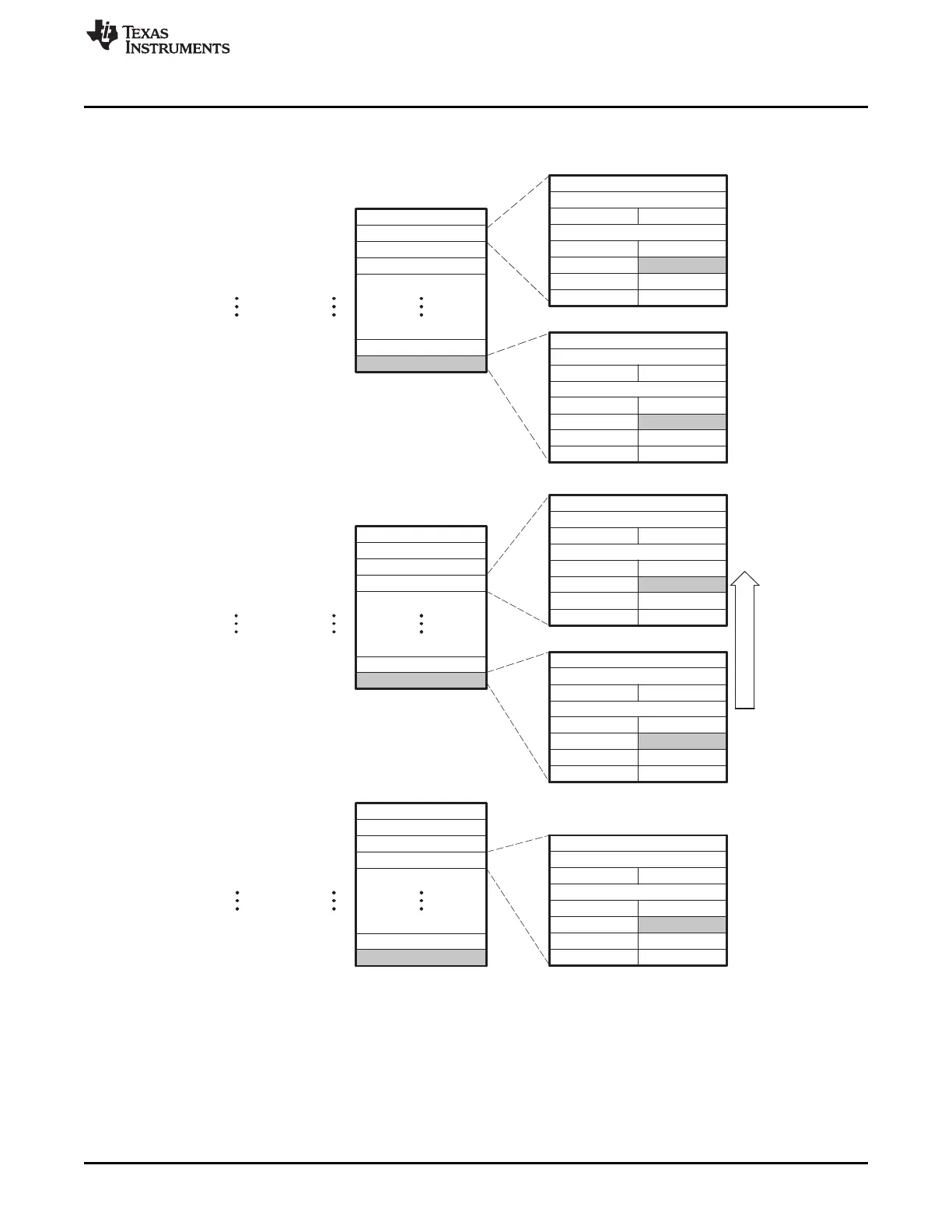

Parameter set 0

PaRAM

Set

#

Byte

address

0EDMA Base Address + 4000h

EDMA Base Address + 4020h 1 Parameter set 1

EDMA Base Address + 4040h 2 Parameter set 2

EDMA Base Address + 4060h 3 Parameter set 3

EDMA Base Address + 5FC0h

EDMA Base Address + 5FE0h

254

255 Parameter set 255

Parameter set 254

OPT X

SRC X

BCNT X ACNT X

DST X

SRCBIDX XDSTBIDX X

Link=5FE0hBCNTRLD X

CCNT X

SRCCIDX XDSTCIDX X

Rsvd

PaRAM set 3

PaRAM set 255

EDMA Base Address + 5FC0h

EDMA Base Address + 5FE0h

254

255

Parameter set 254

Parameter set 255

Parameter set 00EDMA Base Address + 4000h

EDMA Base Address + 4040h

EDMA Base Address + 4060h

EDMA Base Address + 4020h

2

3

1 Parameter set 1

Parameter set 2

Parameter set 3

Byte

address

Set

#

PaRAM

PaRAM set 3

(a) At initialization

(b) After completion of PaRAM set 3

(link update)

Link

update

EDMA Base Address + 5FC0h 254 Parameter set 254

Parameter set 00EDMA Base Address + 4000h

EDMA Base Address + 4040h

EDMA Base Address + 4060h

EDMA Base Address + 4020h

2

3

1 Parameter set 1

Parameter set 2

Parameter set 3

Byte

address

Set

#

PaRAM

CCNT X

SRCCIDX X

Link=5FE0h

SRCBIDX X

ACNT X

DSTCIDX X

Rsvd

BCNTRLD X

DSTBIDX X

BCNT X

DST X

SRC X

PaRAM set 3

OPT X

EDMA Base Address + 5FE0h 255 Parameter set 255

(c) After completion of PaRAM set 127

(link to self)

OPT X

SRC X

BCNT X ACNT X

DST X

SRCBIDX XDSTBIDX X

Link=5FE0hBCNTRLD X

CCNT X

SRCCIDX XDSTCIDX X

Rsvd

OPT X

SRC X

BCNT X ACNT X

DST X

SRCBIDX XDSTBIDX Y

Link=5FE0hBCNTRLD X

CCNT X

SRCCIDX XDSTCIDX X

Rsvd

PaRAM set 255

CCNT X

SRCCIDX X

Link=5FE0h

SRCBIDX X

ACNT X

DSTCIDX X

Rsvd

BCNTRLD X

DSTBIDX X

BCNT X

DST X

SRC X

OPT X

www.ti.com

Functional Description

Figure 11-12. Link-to-Self Transfer

11.3.4 Initiating a DMA Transfer

There are multiple ways to initiate a programmed data transfer using the EDMA3 channel controller.

Transfers on DMA channels are initiated by three sources.

They are listed as follows:

• Event-triggered transfer request (this is the more typical usage of EDMA3): A peripheral, system, or

externally-generated event triggers a transfer request.

• Manually-triggered transfer request:The CPU to manually triggers a transfer by writing a 1 to the

893

SPRUH73H–October 2011–Revised April 2013 Enhanced Direct Memory Access (EDMA)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...