32 32 32 32

L4_PER

L3S

32

L4_FAST

32

L4_WKUP

M3

32

DCAN0

DCAN1

DMTIMER2

DMTIMER3

DMTIMER4

DMTIMER5

DMTIMER6

DMTIMER7

eCAP/eQEP/ePWM0

eCAP/eQEP/ePWM1

eCAP/eQEP/ePWM2

eFuse Ctl

ELM

GPIO1

GPIO2

GPIO3

I2C1

I2C2

IEEE1500

LCD Ctlr

Mailbox0

McASP0 CFG

McASP1 CFG

MMCHS0

MMCHS1

OCP Watchpoint

SPI0

SPI1

Spinlock

UART1

UART2

UART3

UART4

UART5

PRU-ICSS

GEMAC

ADC_TSC

Control Module

DMTIMER0

DMTIMER1_1MS

GPIO0

I2C0

M3 UMEM

M3 DMEM

SmartReflex 0

SmartReflex 1

UART0

WDT1

RTC

PRCM

DebugSS

HWMaster1

Introduction

www.ti.com

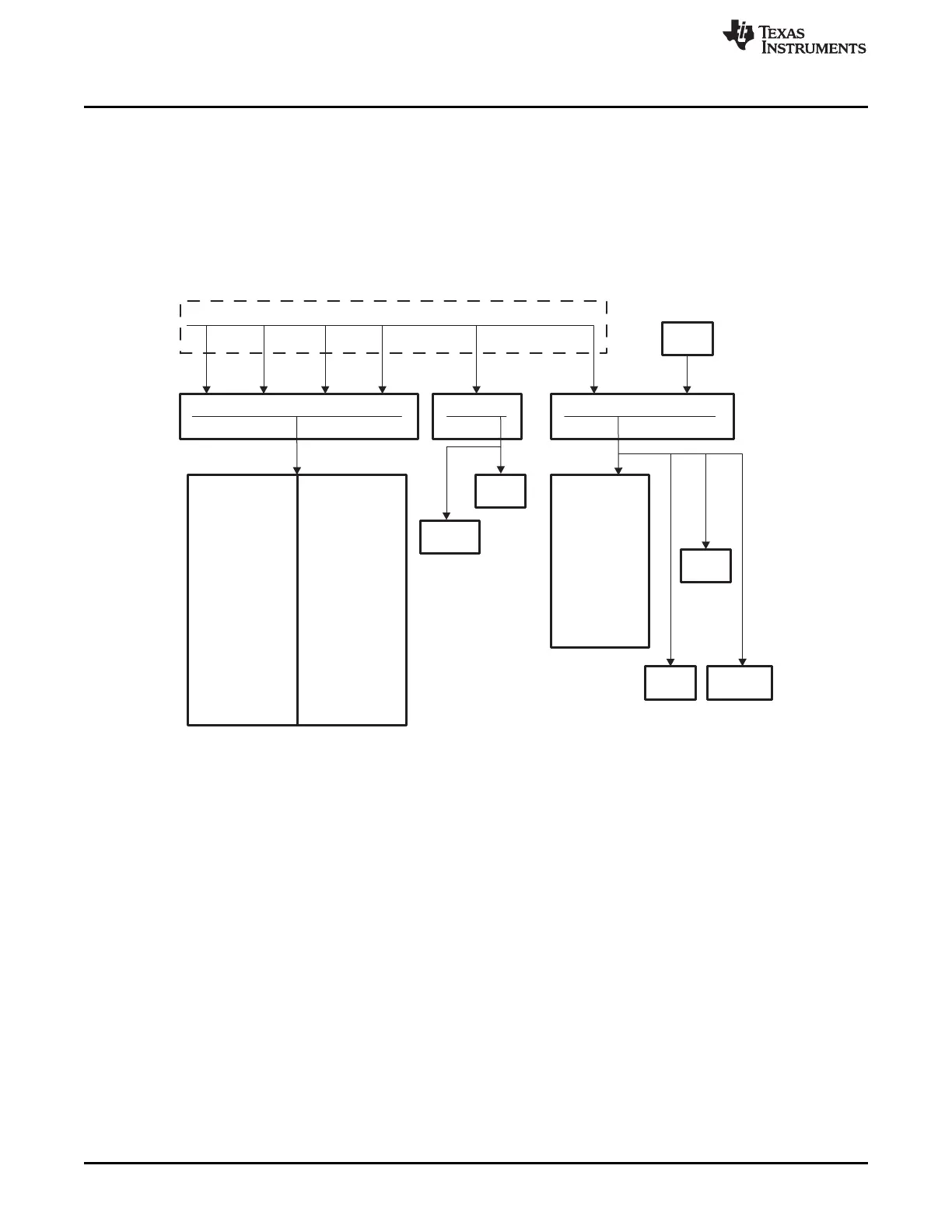

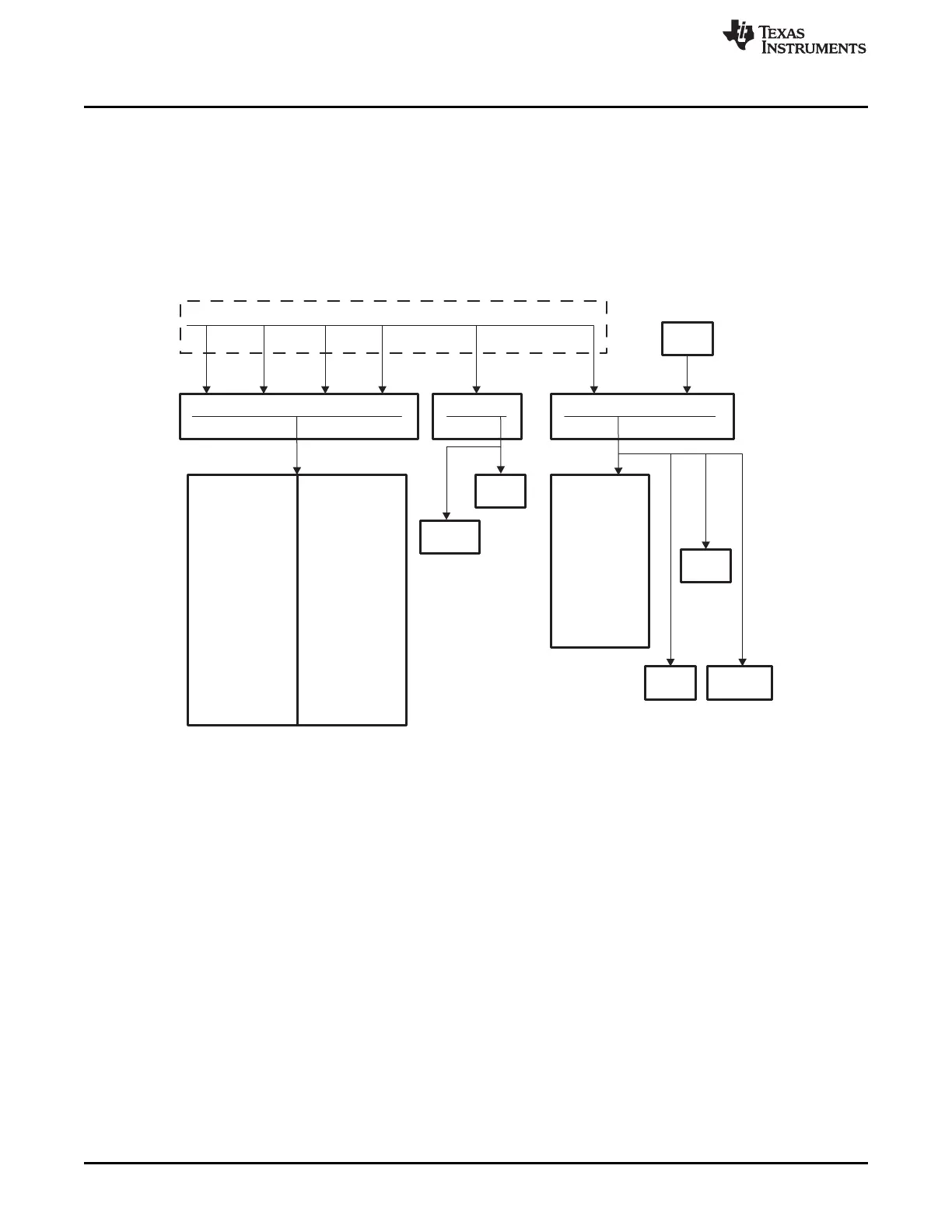

10.1.3 L4 Interconnect

The L4 interconnect is a non-blocking peripheral interconnect that provides low latency access to a large

number of low bandwidth, physically dispersed target cores. The L4 can handle incoming traffic from up to

four initiators and can distribute those communication requests to and collect related responses from up to

63 targets.

This device provides three interfaces with L3 interconnect for High Speed Peripheral, Standard Peripheral,

and Wakeup Peripherals. . Figure 10-2 shows the L4 bus architecture and memory-mapped peripherals.

Figure 10-2. L4 Topology

868

Interconnects SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...