www.ti.com

I2C Registers

21.4.1.1 I2C_REVNB_LO Register (offset = 00h) [reset = 0h]

I2C_REVNB_LO is shown in Figure 21-16 and described in Table 21-9.

This read-only register contains the hard-coded revision number of the module. A write to this register has

no effect. I2C controller with interrupt using interrupt vector register (I2C_IV) is revision 1.x. I2C controller

with interrupt using status register bits (I2C_IRQSTATUS_RAW) is revision 2.x.

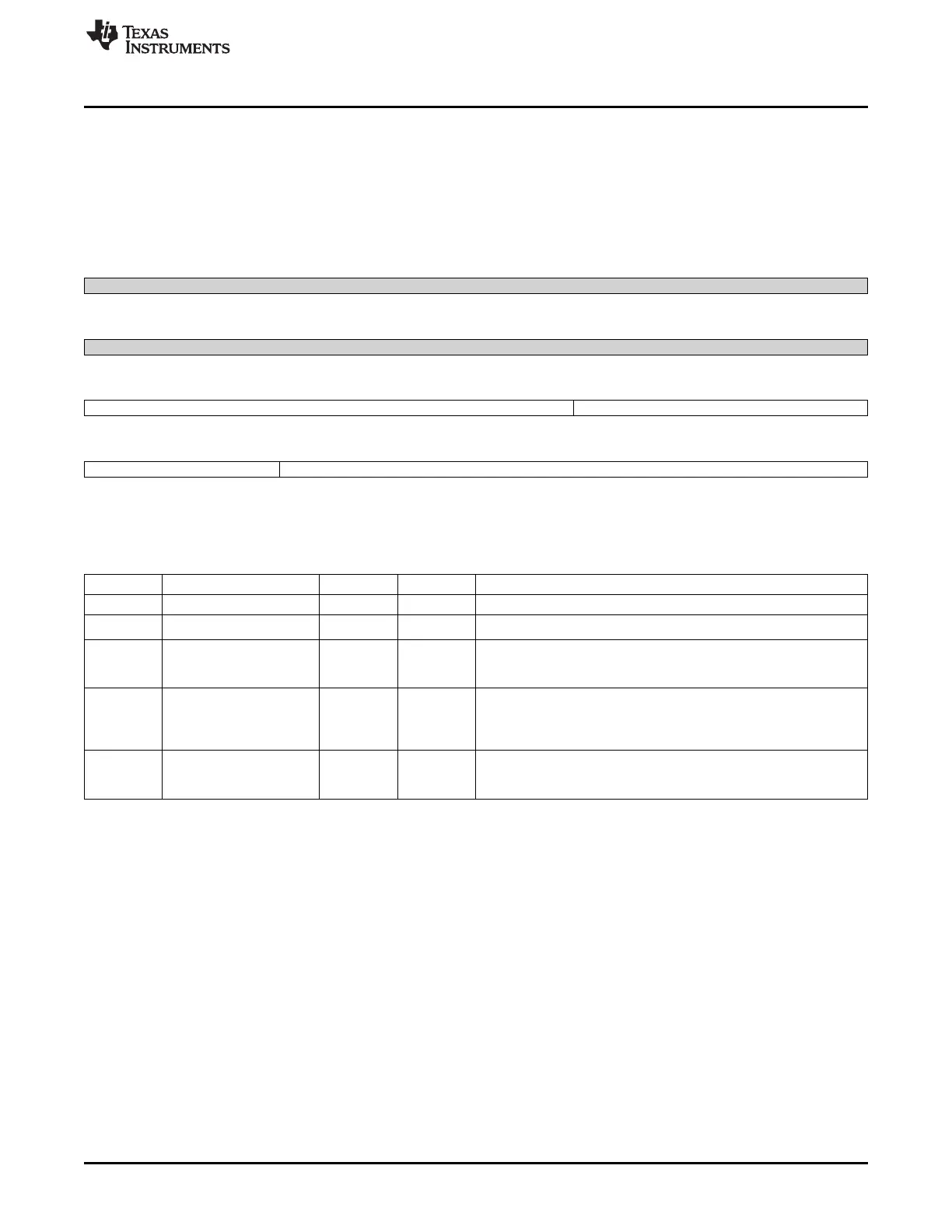

Figure 21-16. I2C_REVNB_LO Register

31 30 29 28 27 26 25 24

Reserved

R-0h

23 22 21 20 19 18 17 16

Reserved

R-0h

15 14 13 12 11 10 9 8

RTL MAJOR

R-0h R-0h

7 6 5 4 3 2 1 0

CUSTOM MINOR

R-0h R-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

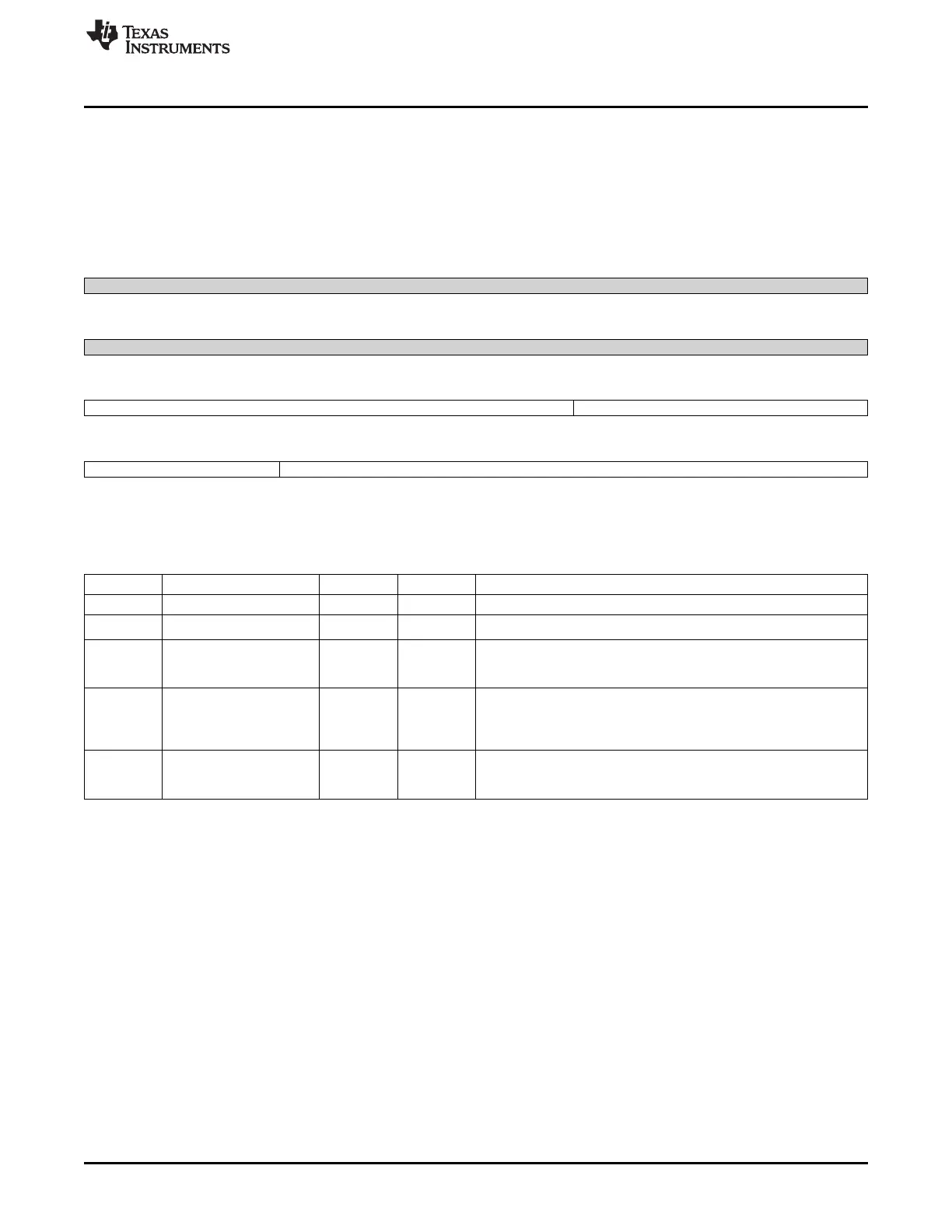

Table 21-9. I2C_REVNB_LO Register Field Descriptions

Bit Field Type Reset Description

31-16 Reserved R 0h

15-11 RTL R 0h

RTL version.

10-8 MAJOR R 0h Major Revision.

This field changes when there is a major feature change.

This field does not change due to bug fix, or minor feature change.

7-6 CUSTOM R 0h Indicates a special version for a particular device.

Consequence of use may avoid use of standard Chip Support

Library (CSL) / Drivers.

0 if non-custom.

5-0 MINOR R 0h Minor Revision This field changes when features are scaled up or

down.

This field does not change due to bug fix, or major feature change.

3717

SPRUH73H–October 2011–Revised April 2013 I2C

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...