www.ti.com

EDMA3 Registers

11.4.1.4.4 EDMA3CC Status Register (CCSTAT)

The EDMA3CC status register (CCSTAT) has a number of status bits that reflect which parts of the

EDMA3CC logic is active at any given instant of time. The CCSTAT is shown in Figure 11-65 and

described in Table 11-49.

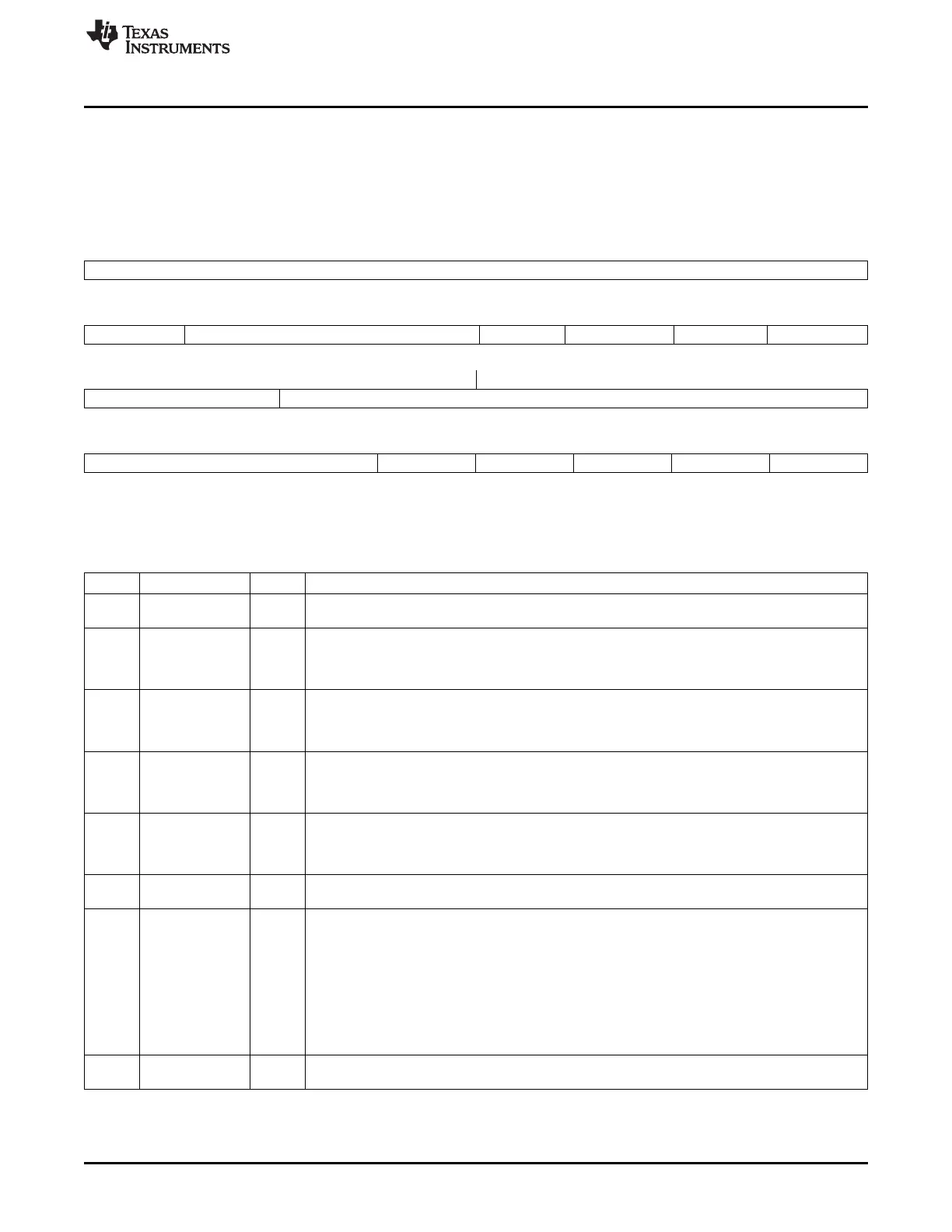

Figure 11-65. EDMA3CC Status Register (CCSTAT)

31 24

Reserved

R-0

23 22 21 20 19 18 17 16

Reserved Reserved QUEACTV3 QUEACTV2 QUEACTV1 QUEACTV0

R-0 R-0 R-0 R-0 R-0 R-0

15 14 13 12 11 10 9 8

Reserved COMPACTV

R-0 R-0

7 6 5 4 3 2 1 0

Reserved ACTV Reserved TRACTV QEVTACTV EVTACTV

R-0 R-0 R-0 R-0 R-0 R-0

LEGEND: R = Read only; -n = value after reset

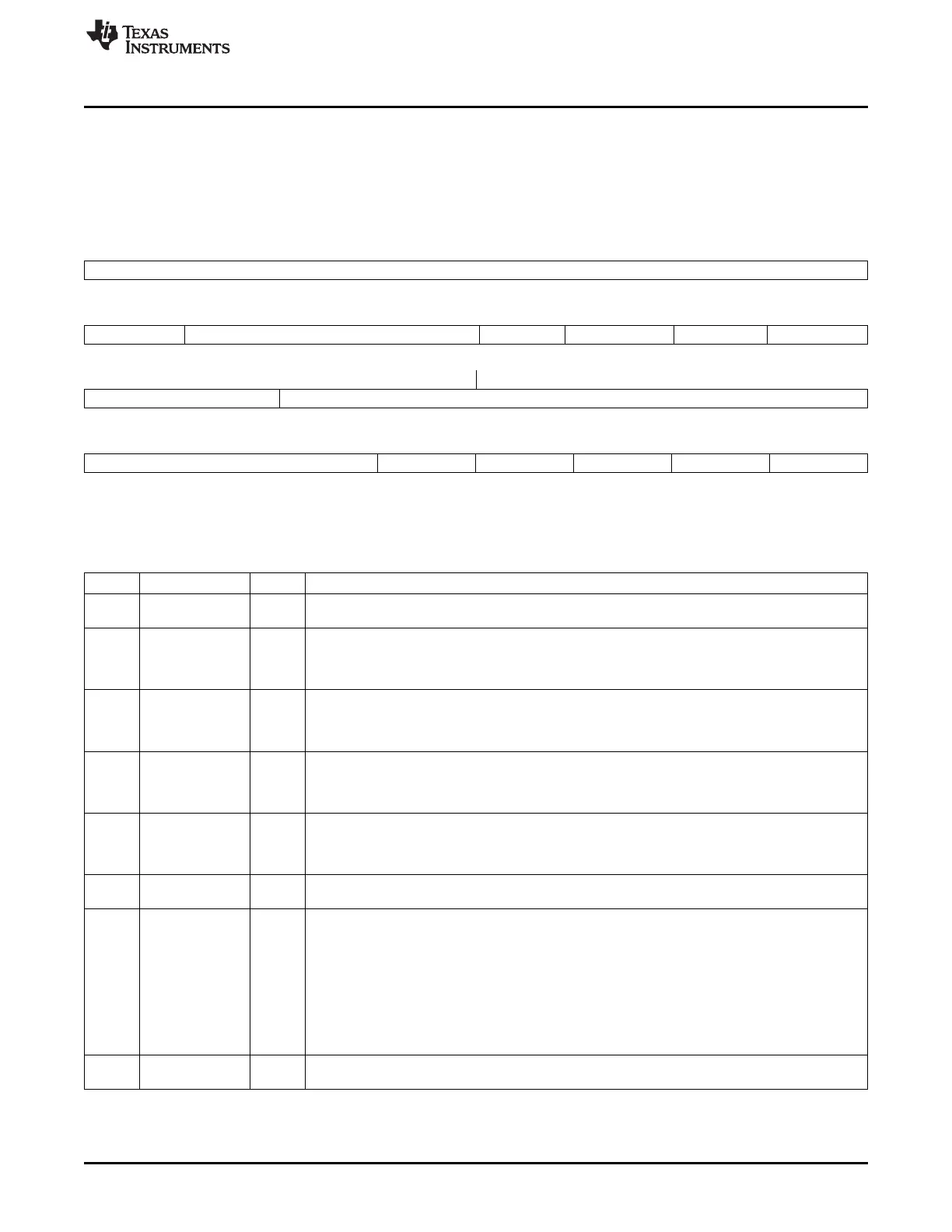

Table 11-49. EDMA3CC Status Register (CCSTAT) Field Descriptions

Bit Field Value Description

31-20 Reserved 0 Reserved. Always write 0 to this bit; writes of 1 to this bit are not supported and attempts to do so

may result in undefined behavior.

19 QUEACTV3 Queue 3 active.

0 No events are queued in queue 3.

1 At least one TR is queued in queue 3.

18 QUEACTV2 Queue 2 active.

0 No events are queued in queue 2.

1 At least one TR is queued in queue 2.

17 QUEACTV1 Queue 1 active.

0 No events are queued in queue 1.

1 At least one TR is queued in queue 1.

16 QUEACTV0 Queue 0 active.

0 No events are queued in queue 0.

1 At least one TR is queued in queue 0.

15-14 Reserved 0 Reserved. Always write 0 to this bit; writes of 1 to this bit are not supported and attempts to do so

may result in undefined behavior.

13-8 COMPACTV 0-3Fh Completion request active. The COMPACTV field reflects the count for the number of completion

requests submitted to the transfer controllers. This count increments every time a TR is submitted

and is programmed to report completion (the TCINTEN or TCCCHEN bits in OPT in the parameter

entry associated with the TR are set). The counter decrements for every valid TCC received back

from the transfer controllers. If at any time the count reaches a value of 63, the EDMA3CC will not

service any new TRs until the count is less then 63 (or return a transfer completion code from a

transfer controller, which would decrement the count).

0 No completion requests outstanding.

1h-3Fh Total of 1 completion request to 63 completion requests are outstanding.

7-5 Reserved 0 Reserved. Always write 0 to this bit; writes of 1 to this bit are not supported and attempts to do so

may result in undefined behavior.

963

SPRUH73H–October 2011–Revised April 2013 Enhanced Direct Memory Access (EDMA)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...