EDMA3 Registers

www.ti.com

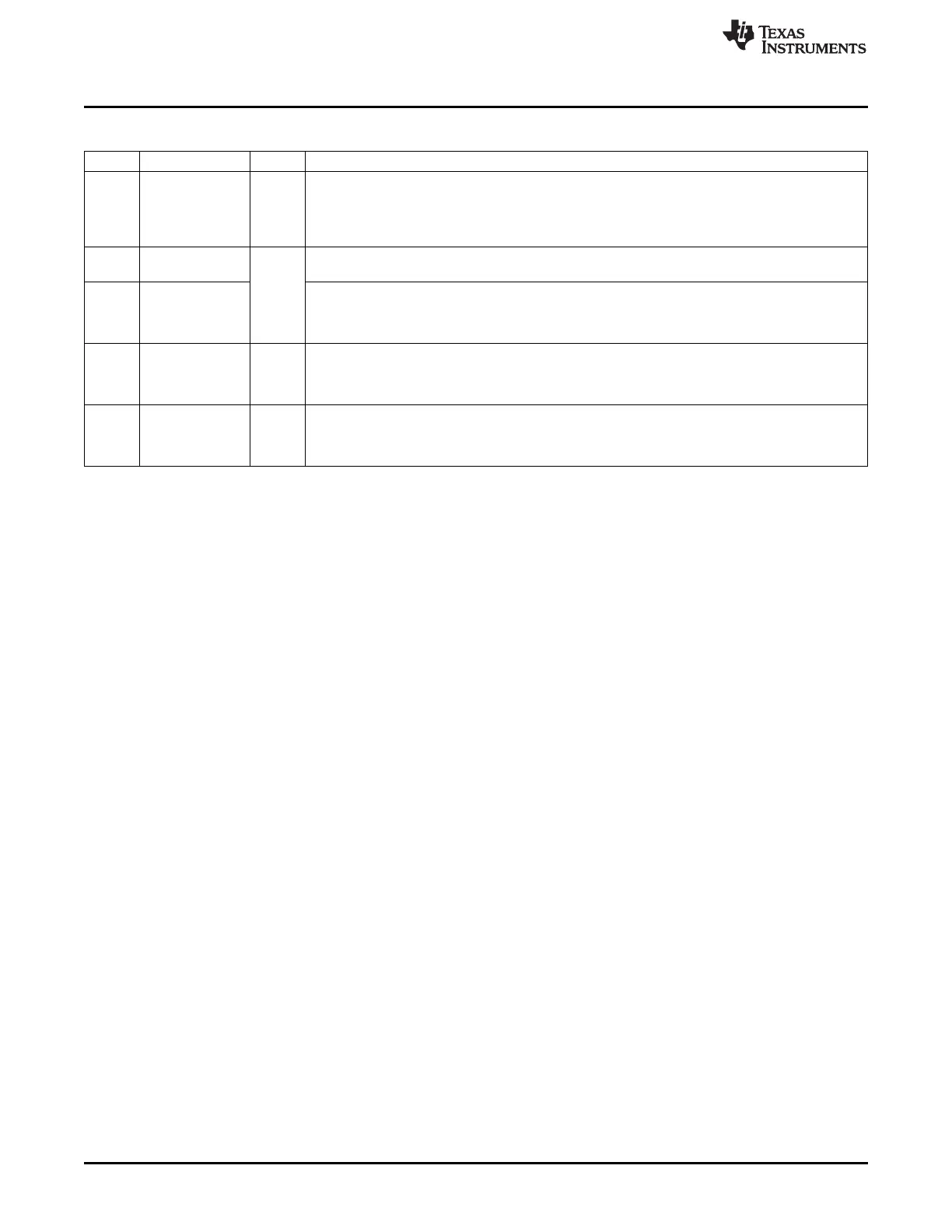

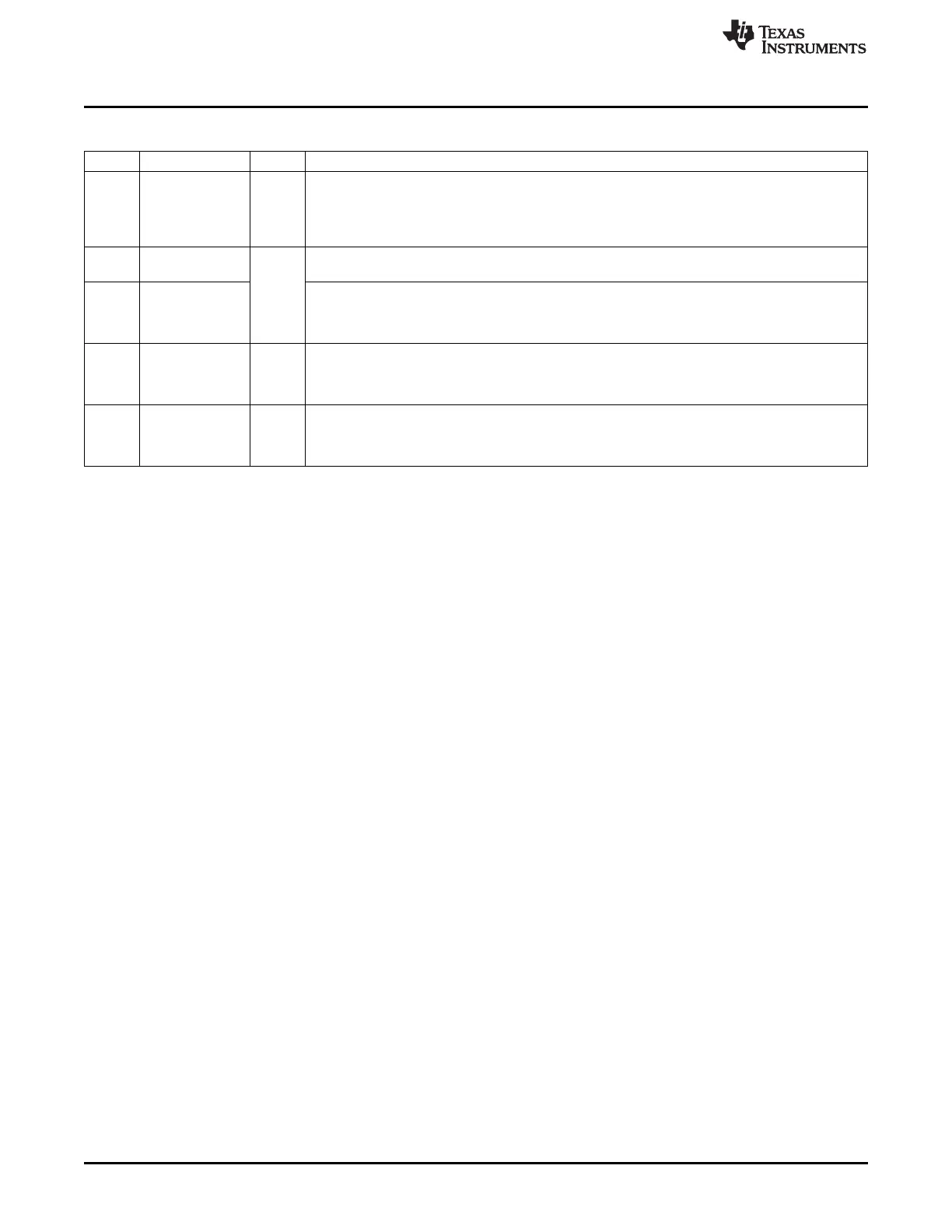

Table 11-49. EDMA3CC Status Register (CCSTAT) Field Descriptions (continued)

Bit Field Value Description

4 ACTV Channel controller active. Channel controller active is a logical-OR of each of the *ACTV bits. The

ACTV bit remains high through the life of a TR.

0 Channel is idle..

1 Channel is busy.

3 Reserved 0 Reserved. Always write 0 to this bit; writes of 1 to this bit are not supported and attempts to do so

may result in undefined behavior.

2 TRACTV Transfer request active.

0 Transfer request processing/submission logic is inactive.

1 Transfer request processing/submission logic is active.

1 QEVTACTV QDMA event active.

0 No enabled QDMA events are active within the EDMA3CC.

1 At least one enabled QDMA event (QER) is active within the EDMA3CC.

0 EVTACTV DMA event active.

0 No enabled DMA events are active within the EDMA3CC.

1 At least one enabled DMA event (ER and EER, ESR, CER) is active within the EDMA3CC.

964

Enhanced Direct Memory Access (EDMA) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...