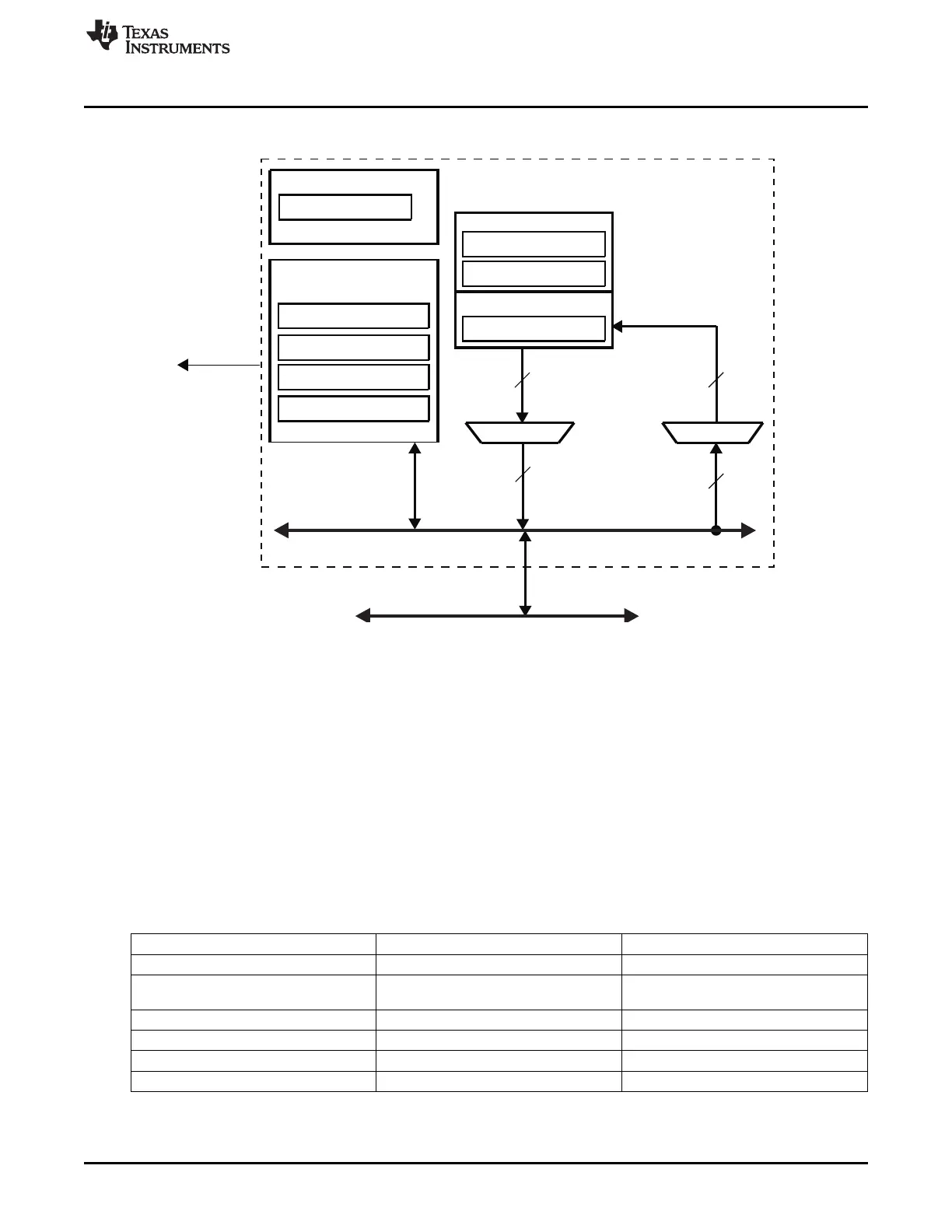

32

Message out Message in

Mailbox m

4 message FIFO

Local interface

Mailbox

Interconnect

32

32

32

MAILBOX_SYSCONFIG

System register

MAILBOX_IRQENABLE_CLR_u

MAILBOX_IRQENABLE_SET_u

MAILBOX_MSGSTATUS_m

MAILBOX_FIFOSTATUS_m

MAILBOX_MESSAGE_m

MAILBOX_IRQSTATUS_CLR_u

MAILBOX_IRQSTATUS_RAW_u

Interrupt registers

Interrupt

requests

www.ti.com

Mailbox

Figure 17-2. Mailbox Block Diagram

17.1.3.2 Software Reset

The mailbox module supports a software reset through the MAILBOX_SYSCONFIG[0].SOFTRESET bit.

Setting this bit to 1 enables an active software reset that is functionally equivalent to a hardware reset.

Reading the MAILBOX_SYSCONFIG[0] SOFTRESET bit gives the status of the software reset:

• Read 1: the software reset is on-going

• Read 0: the software reset is complete

The software must ensure that the software reset completes before doing mailbox operations.

17.1.3.3 Power Management

Table 17-4 describes power-management features available for the mailbox module.

Table 17-4. Local Power Management Features

Feature Registers Description

Clock autogating NA Feature not available

Slave idle modes MAILBOX_SYSCONFIG[3:2].SIDLEMOD Force-idle, no-idle and smart-idle modes

E are available

Clock activity NA Feature not available

Master standby modes NA Feature not available

Global wake-up enable NA Feature not available

Wake-up sources enable NA Feature not available

3239

SPRUH73H–October 2011–Revised April 2013 Interprocessor Communication

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...