www.ti.com

Functional Description

19.3.8.1.2 Choosing the Appropriate Divisor Value

Two divisor values are:

• UART 16x mode: Divisor value = Operating frequency/(16x baud rate)

• UART 13x mode: Divisor value = Operating frequency/(13x baud rate)

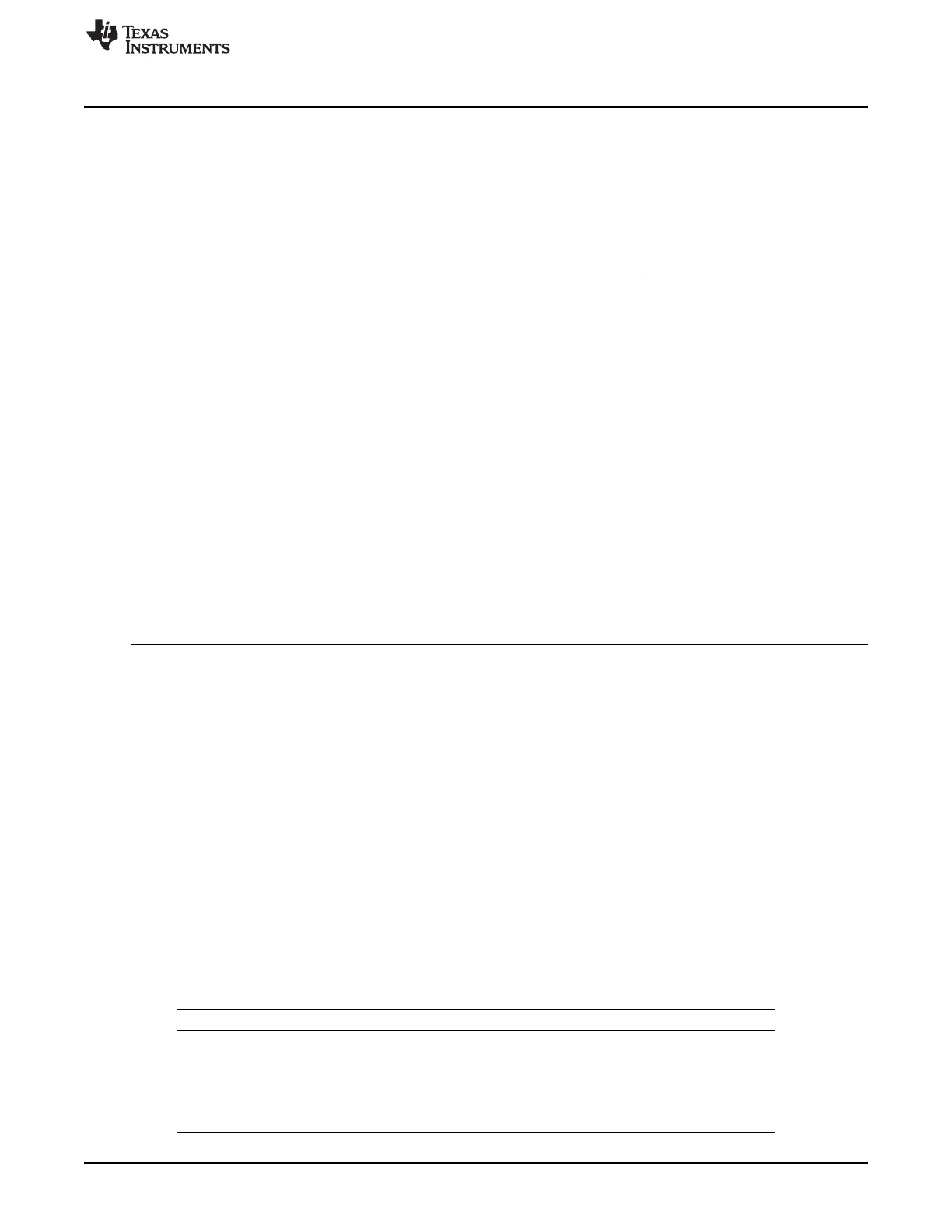

Table 19-25 describes the UART baud rate settings.

Table 19-25. UART Baud Rate Settings (48-MHz Clock)

Baud Rate Baud Multiple DLH,DLL (Decimal) DLH,DLL (Hex) Actual Baud Rate Error (%)

0.3 kbps 16x 10000 0x27, 0x10 0.3 kbps 0

0.6 kbps 16x 5000 0x13, 0x88 0.6 kbps 0

1.2 kbps 16x 2500 0x09, 0xC4 1.2 kbps 0

2.4 kbps 16x 1250 0x04, 0xE2 2.4 kbps 0

4.8 kbps 16x 625 0x02, 0x71 4.8 kbps 0

9.6 kbps 16x 312 0x01, 0x38 9.6153 kbps +0.16

14.4 kbps 16x 208 0x00, 0xD0 14.423 kbps +0.16

19.2 kbps 16x 156 0x00, 0x9C 19.231 kbps +0.16

28.8 kbps 16x 104 0x00, 0x68 28.846 kbps +0.16

38.4 kbps 16x 78 0x00, 0x4E 38.462 kbps +0.16

57.6 kbps 16x 52 0x00, 0x34 57.692 kbps +0.16

115.2 kbps 16x 26 0x00, 0x1A 115.38 kbps +0.16

230.4 kbps 16x 13 0x00, 0x0D 230.77 kbps +0.16

460.8 kbps 13x 8 0x00, 0x08 461.54 kbps +0.16

921.6 kbps 13x 4 0x00, 0x04 923.08 kbps +0.16

1.843 Mbps 13x 2 0x00, 0x02 1.846 Mbps +0.16

3.6884 Mbps 13x 1 0x00, 0x01 3.6923 Mbps +0.16

19.3.8.1.3 UART Data Formatting

The UART can use hardware flow control to manage transmission and reception. Hardware flow control

significantly reduces software overhead and increases system efficiency by automatically controlling serial

data flow using the RTS output and CTS input signals.

The UART is enhanced with the autobauding function. In control mode, autobauding lets the speed, the

number of bits per character, and the parity selected be set automatically.

19.3.8.1.3.1 Frame Formatting

When autobauding is not used, frame format attributes must be defined in the UARTi.UART_LCR register.

Character length is specified using the UARTi.UART_LCR[1:0] CHAR_LENGTH bit field.

The number of stop-bits is specified using the UARTi.UART_LCR[2] NB_STOP bit.

The parity bit is programmed using the UARTi.UART_LCR[5:3] PARITY_EN, PARITY_TYPE_1, and

PARITY_TYPE_2 bit fields (see Table 19-26).

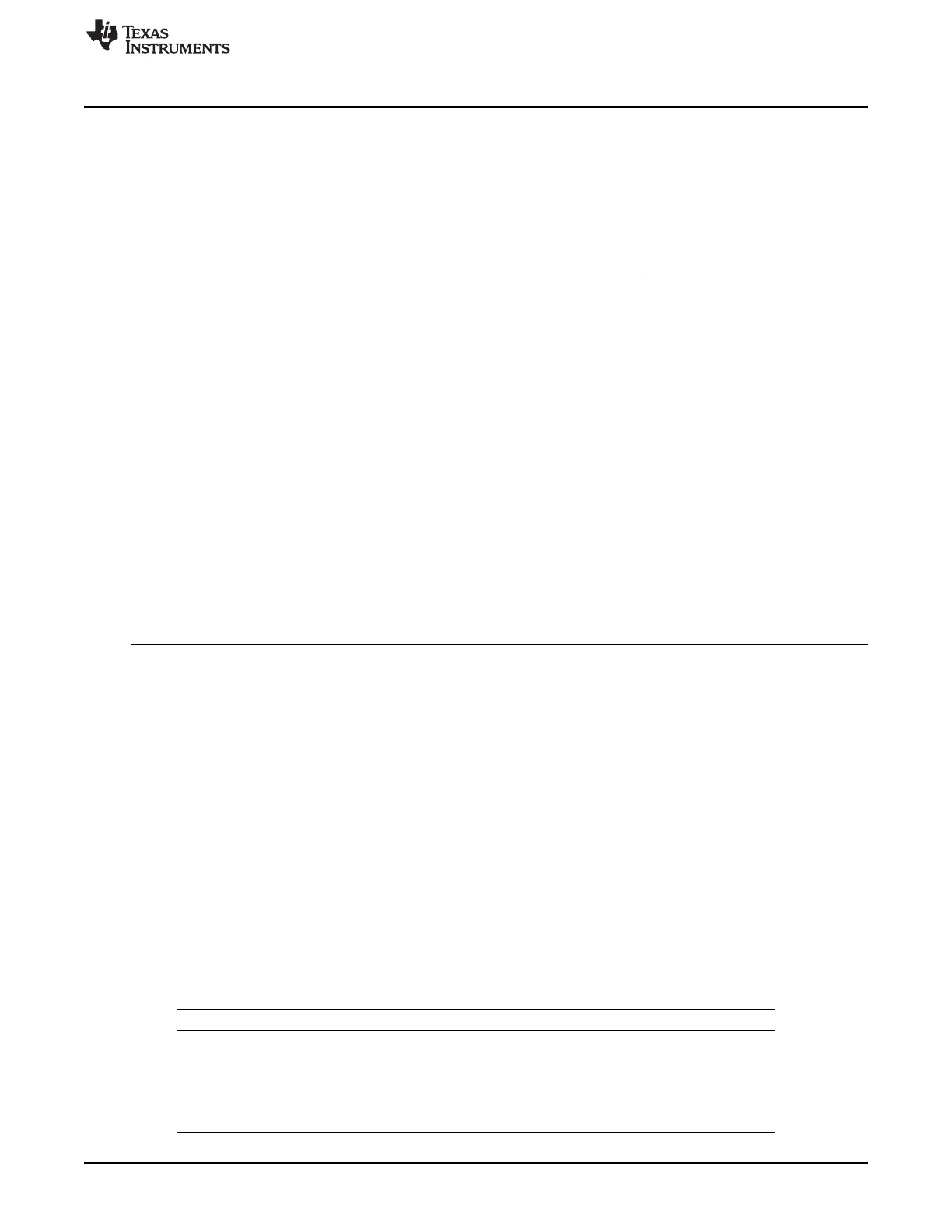

Table 19-26. UART Parity Bit Encoding

PARITY_EN PARITY_TYPE_1 PARITY_TYPE_2 Parity

0 N/A N/A No parity

1 0 0 Odd parity

1 1 0 Even parity

1 0 1 Forced 1

1 1 1 Forced 0

3475

SPRUH73H–October 2011–Revised April 2013 Universal Asynchronous Receiver/Transmitter (UART)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...