Descriptor

Descriptor

Descriptor

Descriptor

Descriptor

Buffer

Buffer

Buffer

Buffer

Buffer

Rx Queue Head Descriptor Pointer

Host

Memory

Port Rx

DMA State

www.ti.com

Software Operation

14.4.2 Receive Operation

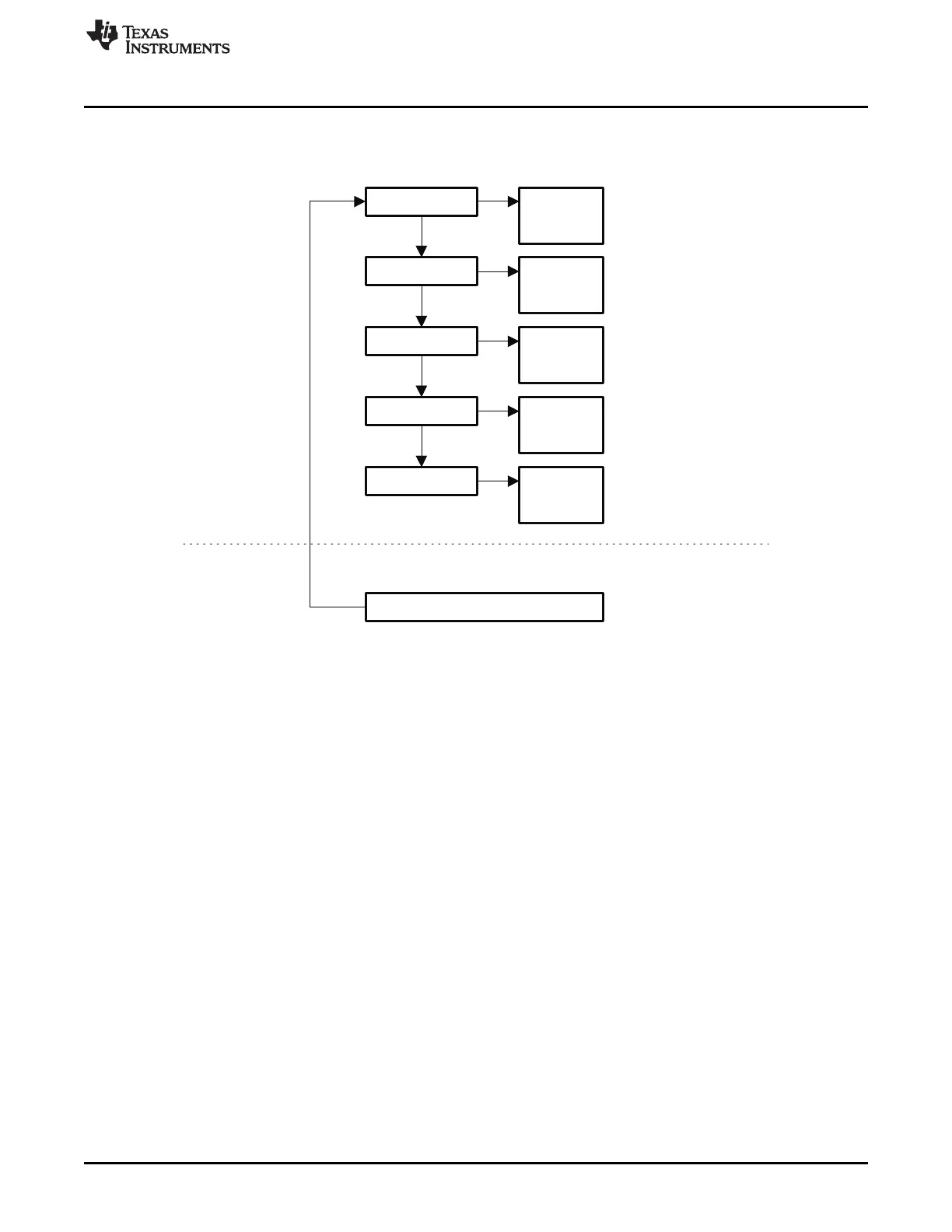

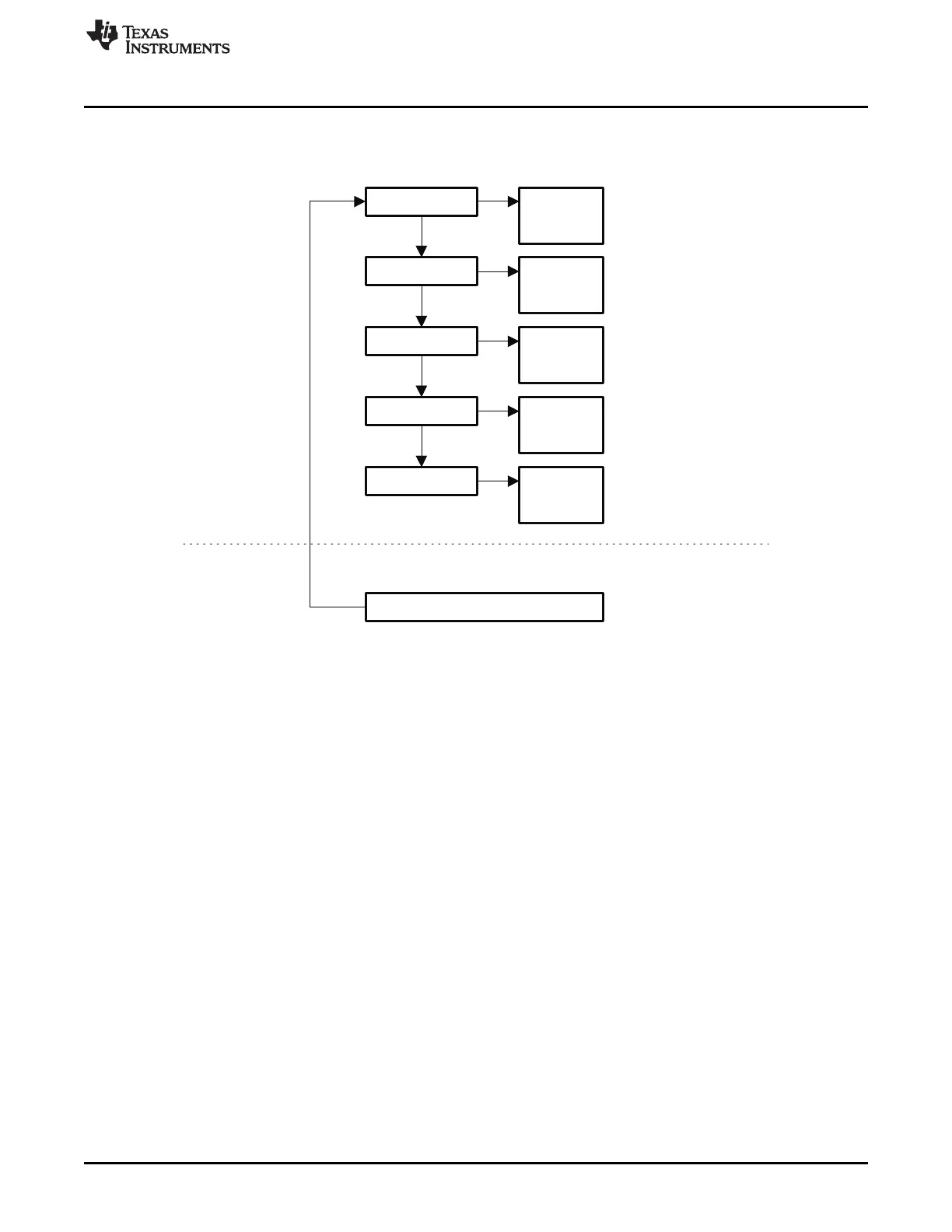

Figure 14-14. Port RX DMA State

After reset the host must write zeroes to all Rx DMA State head descriptor pointers. The Rx port may then

be enabled. To initiate packet reception, the host constructs receive queues in memory and then writes

the appropriate Rx DMA state head descriptor pointer. For each Rx buffer descriptor added to the queue,

the host must initialize the Rx buffer descriptor values as follows:

• Write the Next Descriptor Pointer with the 32-bit aligned address of the next descriptor in the queue

(zero if last descriptor)

• Write the Buffer Pointer with the byte aligned address of the buffer data

• Clear the Offset field

• Write the Buffer Length with the number of bytes in the buffer

• Clear the SOP, EOP, and EOQ bits

• Set the Ownership bit

The host enables packet reception on a given channel by writing the address of the first buffer descriptor

in the queue (nonzero value) to the channel’s head descriptor pointer in the channel’s Rx DMA state.

When packet reception begins on a given channel, the port fills each Rx buffer with data in order starting

with the first buffer and proceeding through the Rx queue. If the Buffer Offset in the Rx DMA State is

nonzero, then the port will begin writing data after the offset number of bytes in the SOP buffer. The port

performs the following operations at the end of each packet reception:

• Overwrite the buffer length in the packet’s EOP buffer descriptor with the number of bytes actually

received in the packet’s last buffer. The host initialized value is the buffer size. The overwritten value

will be less than or equal to the host initialized value.

• Set the EOP bit in the packet’s EOP buffer descriptor.

• Set the EOQ bit in the packet’s EOP buffer descriptor if the current packet is the last packet in the

queue.

• Overwrite the packet’s SOP buffer descriptor Buffer Offset with the Rx DMA state value (the host

initialized the buffer descriptor Buffer Offset value to zero). All non SOP buffer descriptors must have a

zero Buffer Offset initialized by the host.

1237

SPRUH73H–October 2011–Revised April 2013 Ethernet Subsystem

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...