CONTROL_MODULE Registers

www.ti.com

9.3.79 m3_txev_eoi Register (offset = 1324h) [reset = 0h]

m3_txev_eoi is shown in Figure 9-82 and described in Table 9-89.

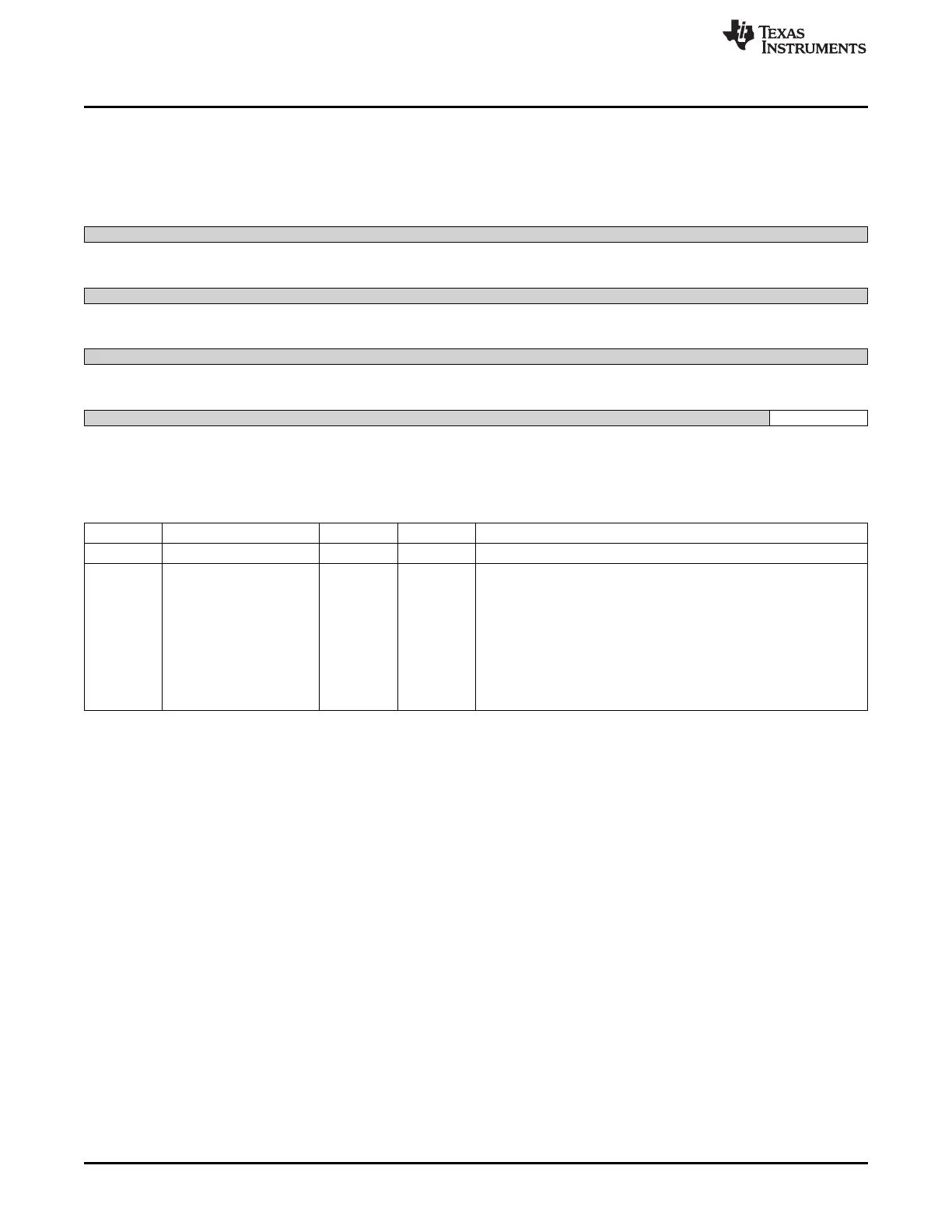

Figure 9-82. m3_txev_eoi Register

31 30 29 28 27 26 25 24

Reserved

R-0h

23 22 21 20 19 18 17 16

Reserved

R-0h

15 14 13 12 11 10 9 8

Reserved

R-0h

7 6 5 4 3 2 1 0

Reserved m3_txev_eoi

R-0h R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

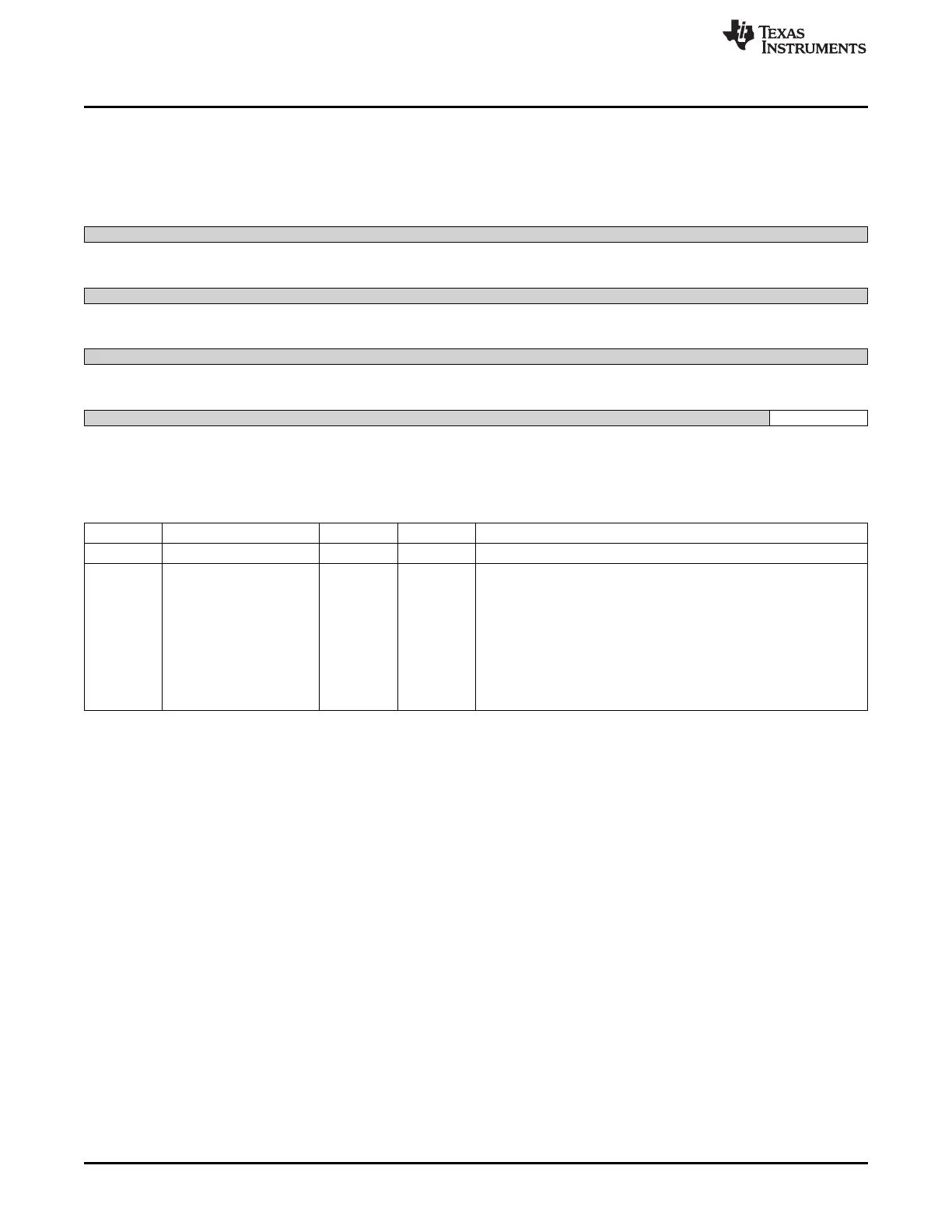

Table 9-89. m3_txev_eoi Register Field Descriptions

Bit Field Type Reset Description

31-1 Reserved R 0h

0 m3_txev_eoi R/W 0h TXEV (Event) from M3 processor is a pulse signal connected as

intertupt to MPU IRQ(78) Since MPU expects level signals.

The TXEV pulse from M3 is converted to a level in glue logic.

The logic works as follows:

-On a 0-1 transition on TXEV, the IRQ[78] is set.

-For clearing the interrupt, S/W must do the following:

S/W must clear the IRQ[78] by writing a 1 to M3_TXEV_EOI bit in

this registe

This bit is sticky and for re-arming the IRQ[78], S/W must write a 0 to

this field in the ISR

844

Control Module SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...