www.ti.com

Enhanced Capture (eCAP) Module

15.3.4.1.8 ECCTL2 Register (offset = 2Ah) [reset = 0h]

ECCTL2 is shown in Figure 15-123 and described in Table 15-116.

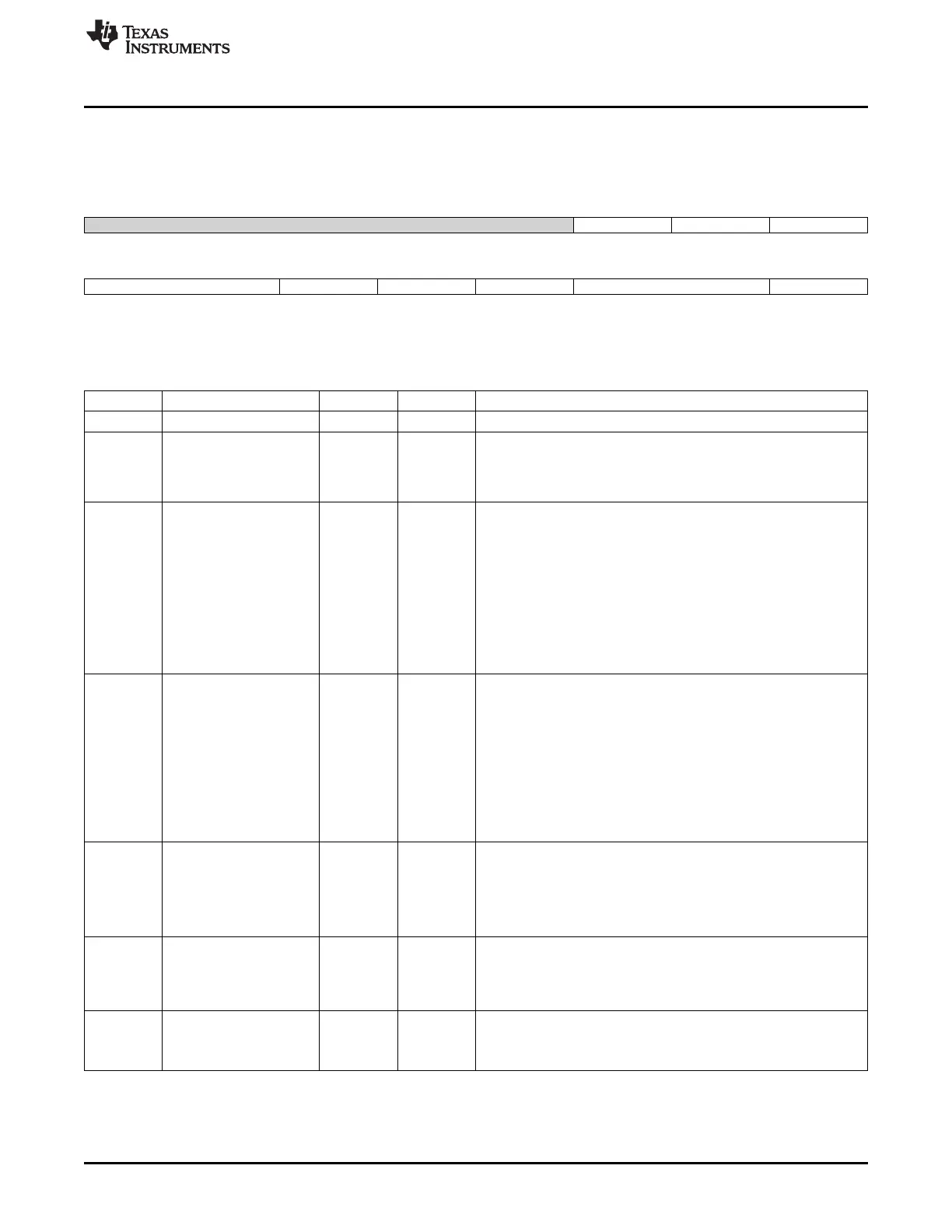

Figure 15-123. ECCTL2 Register

15 14 13 12 11 10 9 8

Reserved APWMPOL CAP_APWM SWSYNC

R-0h R/W-0h R/W-0h R/W-0h

7 6 5 4 3 2 1 0

SYNCO_SEL SYNCI_EN TSCTRSTOP RE-ARM STOP_WRAP CONT_ONESHT

R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

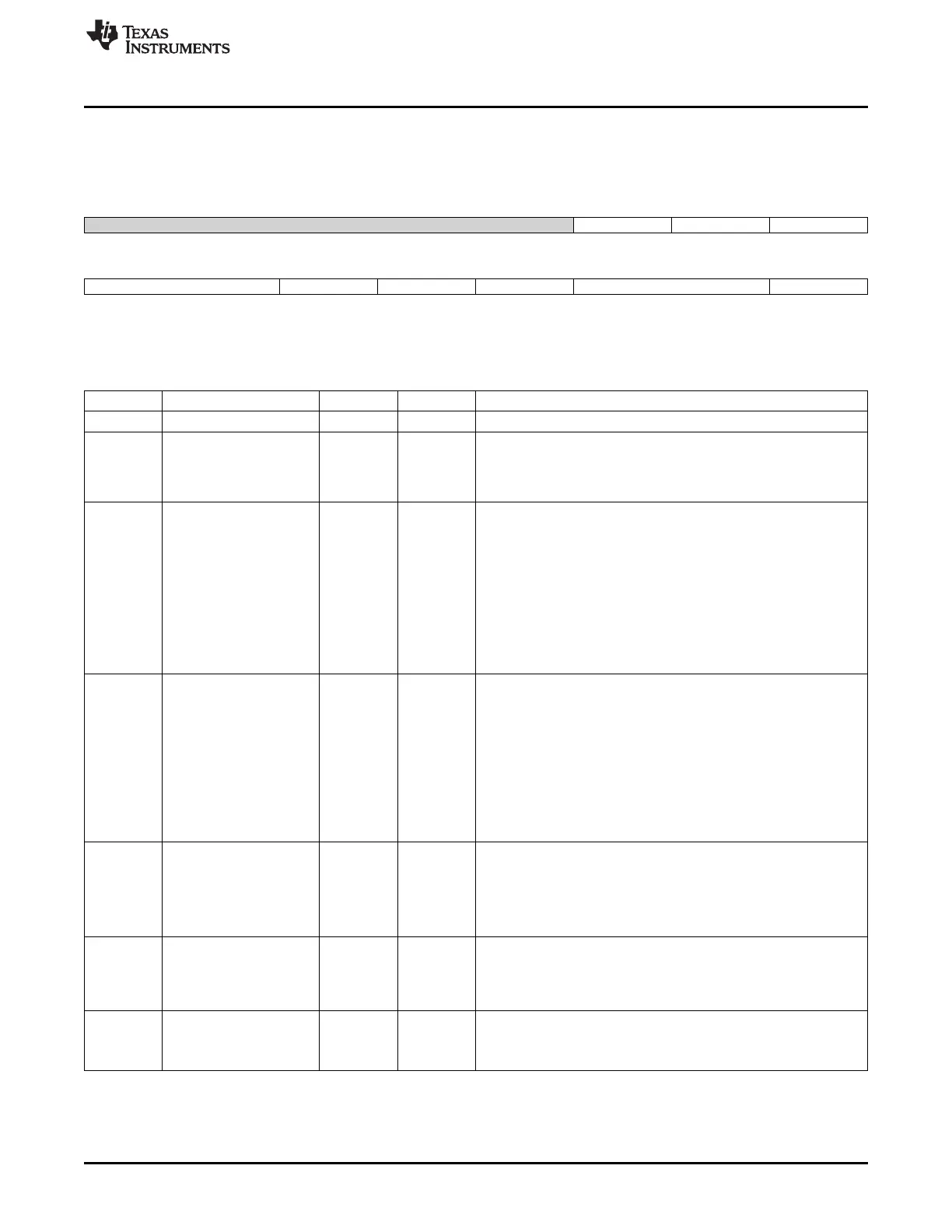

Table 15-116. ECCTL2 Register Field Descriptions

Bit Field Type Reset Description

15-11 Reserved R 0h

10 APWMPOL R/W 0h APWM output polarity select.

This is applicable only in APWM operating mode

0x0 = Output is active high (Compare value defines high time)

0x1 = Output is active low (Compare value defines low time)

9 CAP_APWM R/W 0h

CAP/APWM operating mode select

0x0 = ECAP module operates in capture mode. This mode forces

the following configuration: Inhibits TSCTR resets via PRDEQ event.

Inhibits shadow loads on CAP1 and 2 registers. Permits user to

enable CAP1-4 register load. ECAPn/APWMn pin operates as a

capture input.

0x1 = ECAP module operates in APWM mode. This mode forces the

following configuration: Resets TSCTR on PRDEQ event (period

boundary). Permits shadow loading on CAP1 and 2 registers.

Disables loading of time-stamps into CAP1-4 registers.

ECAPn/APWMn pin operates as a APWM output.

8 SWSYNC R/W 0h Software-forced Counter (TSCTR) Synchronizing.

This provides a convenient software method to synchronize some or

all ECAP time bases.

In APWM mode, the synchronizing can also be done via the PRDEQ

event.

Note: Selecting PRDEQ is meaningful only in APWM mode.

However, you can choose it in CAP mode if you find doing so useful.

0x0 = Writing a zero has no effect. Reading always returns a zero

0x1 = Writing a one forces a TSCTR shadow load of current ECAP

module and any ECAP modules down-stream providing the

SYNCO_SEL bits are 0,0. After writing a 1, this bit returns to a zero.

7-6 SYNCO_SEL R/W 0h

Sync-Out Select

0x0 = Select sync-in event to be the sync-out signal (pass through)

0x1 = Select PRDEQ event to be the sync-out signal

0x2 = Disable sync out signal

0x3 = Disable sync out signal

5 SYNCI_EN R/W 0h

Counter (TSCTR) Sync-In select mode

0x0 = Disable sync-in option

0x1 = Enable counter (TSCTR) to be loaded from CTRPHS register

upon either a SYNCI signal or a S/W force event.

4 TSCTRSTOP R/W 0h

Time Stamp (TSCTR) Counter Stop (freeze) Control

0x0 = TSCTR stopped

0x1 = TSCTR free-running

1643

SPRUH73H–October 2011–Revised April 2013 Pulse-Width Modulation Subsystem (PWMSS)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...