EDMA3 Registers

www.ti.com

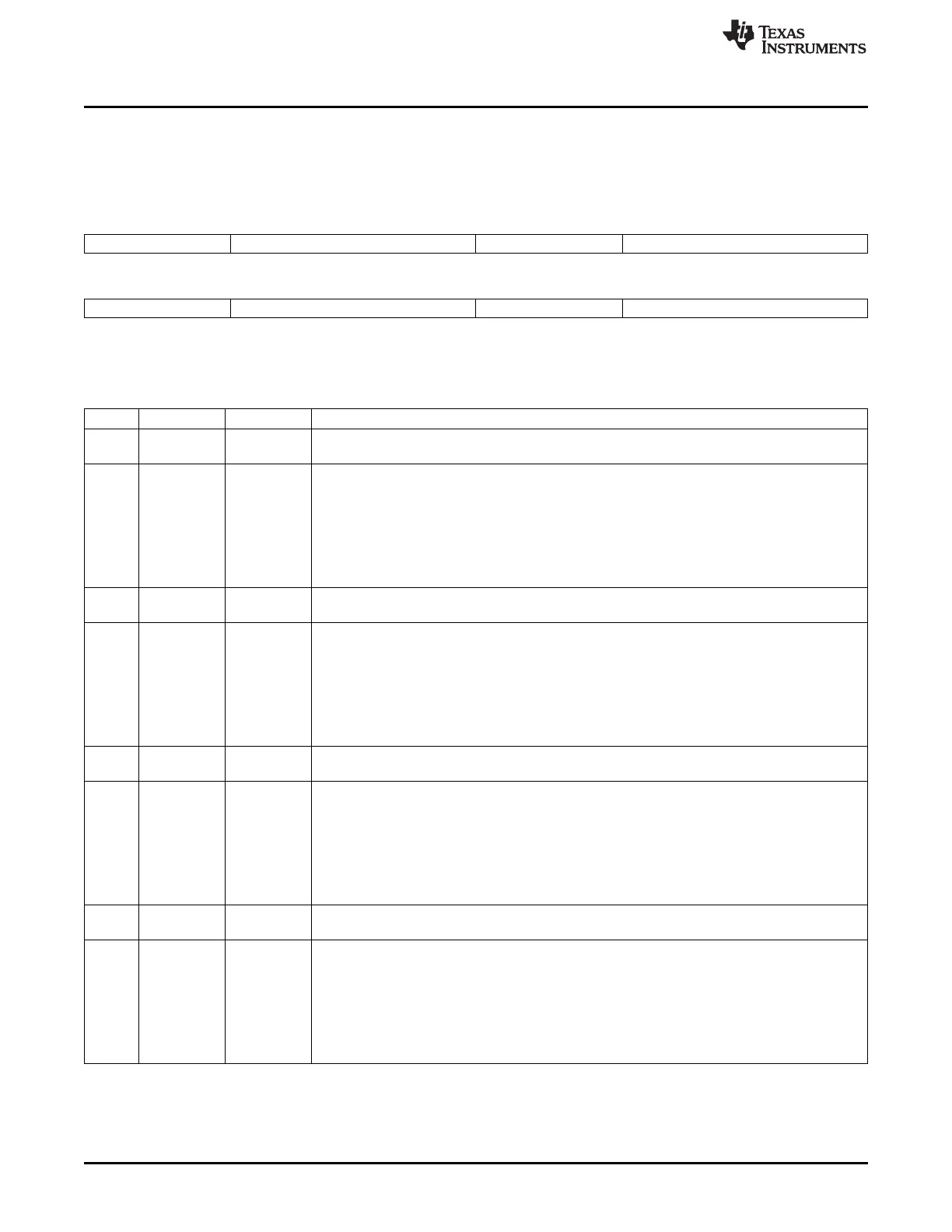

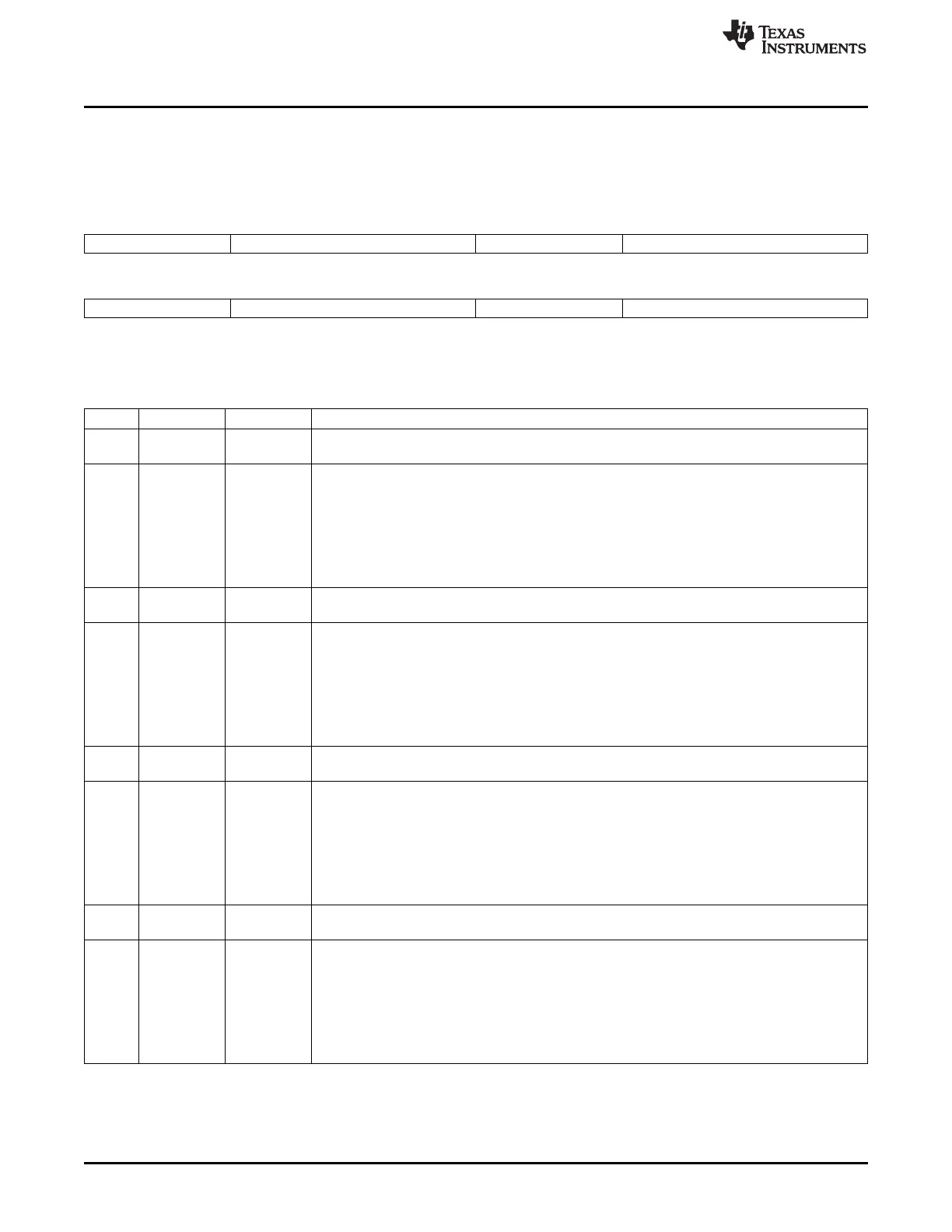

11.4.1.4.3 Queue Watermark Threshold A Register (QWMTHRA)

The queue watermark threshold A register (QWMTHRA) is shown in Figure 11-64 and described in

Table 11-48.

Figure 11-64. Queue Watermark Threshold A Register (QWMTHRA)

31 29 28 24 23 21 20 16

Reserved Q3 Reserved Q2

R-0 R/W-10 R-0 R/W-10

15 13 12 8 7 5 4 0

Reserved Q1 Reserved Q0

R-0 R/W-10h R-0 R/W-10h

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 11-48. Queue Watermark Threshold A Register (QWMTHRA) Field Descriptions

Bit Field Value Description

31-29 Reserved 0 Reserved. Always write 0 to this bit; writes of 1 to this bit are not supported and attempts to do so

may result in undefined behavior.

28-24 Q3 0-1Fh Queue threshold for queue 3 value. The QTHRXCD3 bit in the EDMA3CC error register (CCERR)

and the THRXCD bit in the queue status register 3 (QSTAT3) are set when the number of events

in queue 3 at an instant in time (visible via the NUMVAL bit in QSTAT3) equals or exceeds the

value specified by Q3.

0-10h The default is 16 (maximum allowed).

11h Disables the threshold errors.

12h-1Fh Reserved.

23-21 Reserved 0 Reserved. Always write 0 to this bit; writes of 1 to this bit are not supported and attempts to do so

may result in undefined behavior.

20-16 Q2 0-1Fh Queue threshold for queue 2 value. The QTHRXCD2 bit in the EDMA3CC error register (CCERR)

and the THRXCD bit in the queue status register 2 (QSTAT2) are set when the number of events

in queue 2 at an instant in time (visible via the NUMVAL bit in QSTAT2) equals or exceeds the

value specified by Q2.

0-10h The default is 16 (maximum allowed).

11h Disables the threshold errors.

12h-1Fh Reserved.

15-13 Reserved 0 Reserved. Always write 0 to this bit; writes of 1 to this bit are not supported and attempts to do so

may result in undefined behavior.

12-8 Q1 Queue threshold for queue 1 value. The QTHRXCD1 bit in the EDMA3CC error register (CCERR)

and the THRXCD bit in the queue status register 1 (QSTAT1) are set when the number of events

in queue 1 at an instant in time (visible via the NUMVAL bit in QSTAT1) equals or exceeds the

value specified by Q1.

0-10h The default is 16 (maximum allowed).

11h Disables the threshold errors.

12h-1Fh Reserved.

7-5 Reserved 0 Reserved. Always write 0 to this bit; writes of 1 to this bit are not supported and attempts to do so

may result in undefined behavior.

4-0 Q0 Queue threshold for queue 0 value. The QTHRXCD0 bit in the EDMA3CC error register (CCERR)

and the THRXCD bit in the queue status register 0 (QSTAT0) are set when the number of events

in queue 0 at an instant in time (visible via the NUMVAL bit in QSTAT0) equals or exceeds the

value specified by Q0.

0-10h The default is 16 (maximum allowed).

11h Disables the threshold errors.

12h-1Fh Reserved.

962

Enhanced Direct Memory Access (EDMA) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...