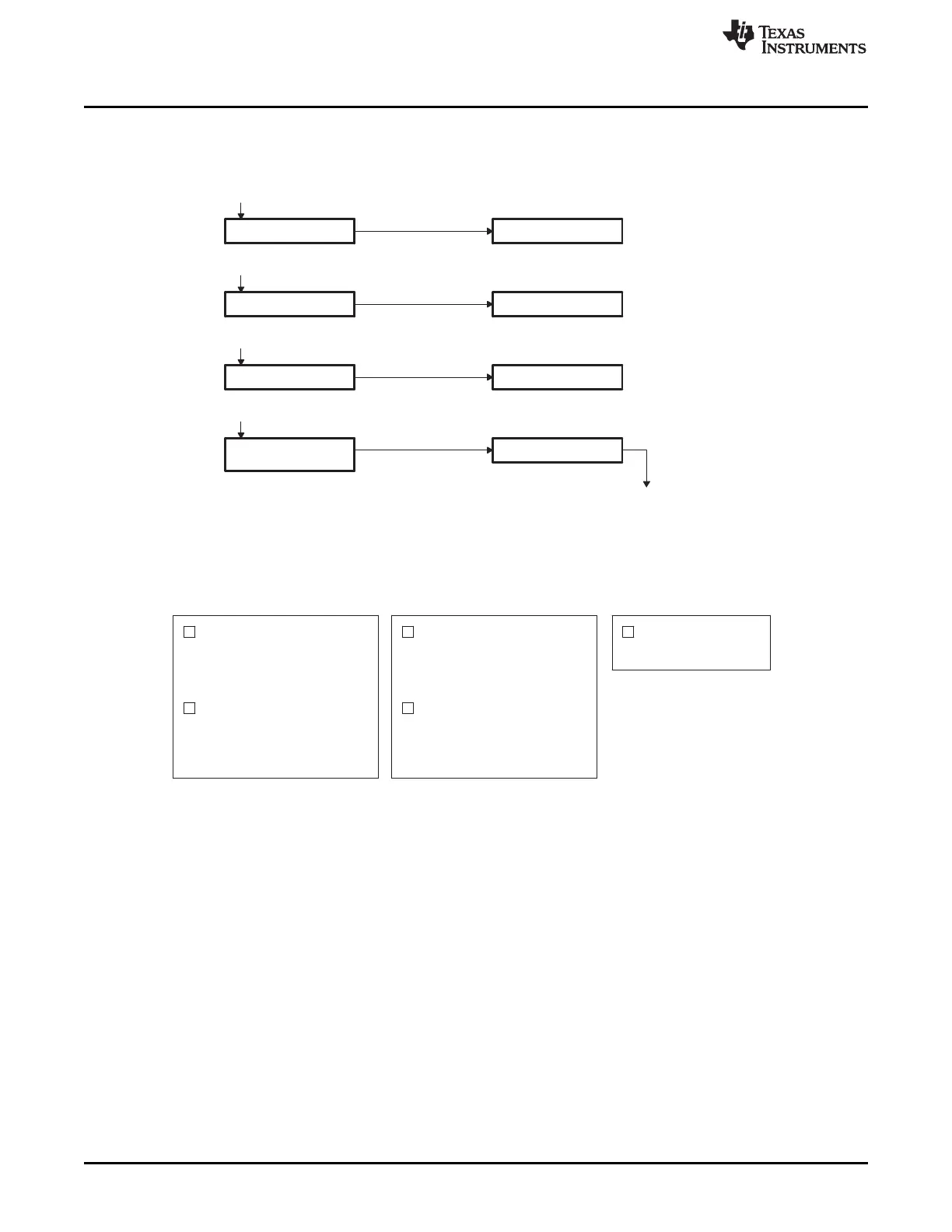

Channel 48, array 0

Intermediate

transfer complete

(A)

Channel 8, array 0

Event 48

Hardwired event

(tied to GPINT0, event 48)

Chained event

(event 8)

Channel 48, array 1

Event 48

Channel 8, array 1

Intermediate

transfer complete

(A)

Channel 8, array 3

Channel 48, array 3

Channel 48, array 2

Event 48

Event 48

Channel 8, array 2

Transfer complete

(B)

Intermediate

transfer complete

(A)

(last array)

Transfer complete sets

IPR.I8 = 1

If IPR.I8 = 1, interrupt

EDMACC_INT* sent

Notes:

(A) Intermediate transfer complete chaining synchronizes event 8

ITCCHEN = 1, TCC = 01000b, and sets CER.E8 = 1

(B) Transfer complete chaining synchronizes event 8

TCCHEN =1, TCC = 01000b and sets CER.E8 = 1

to CPU

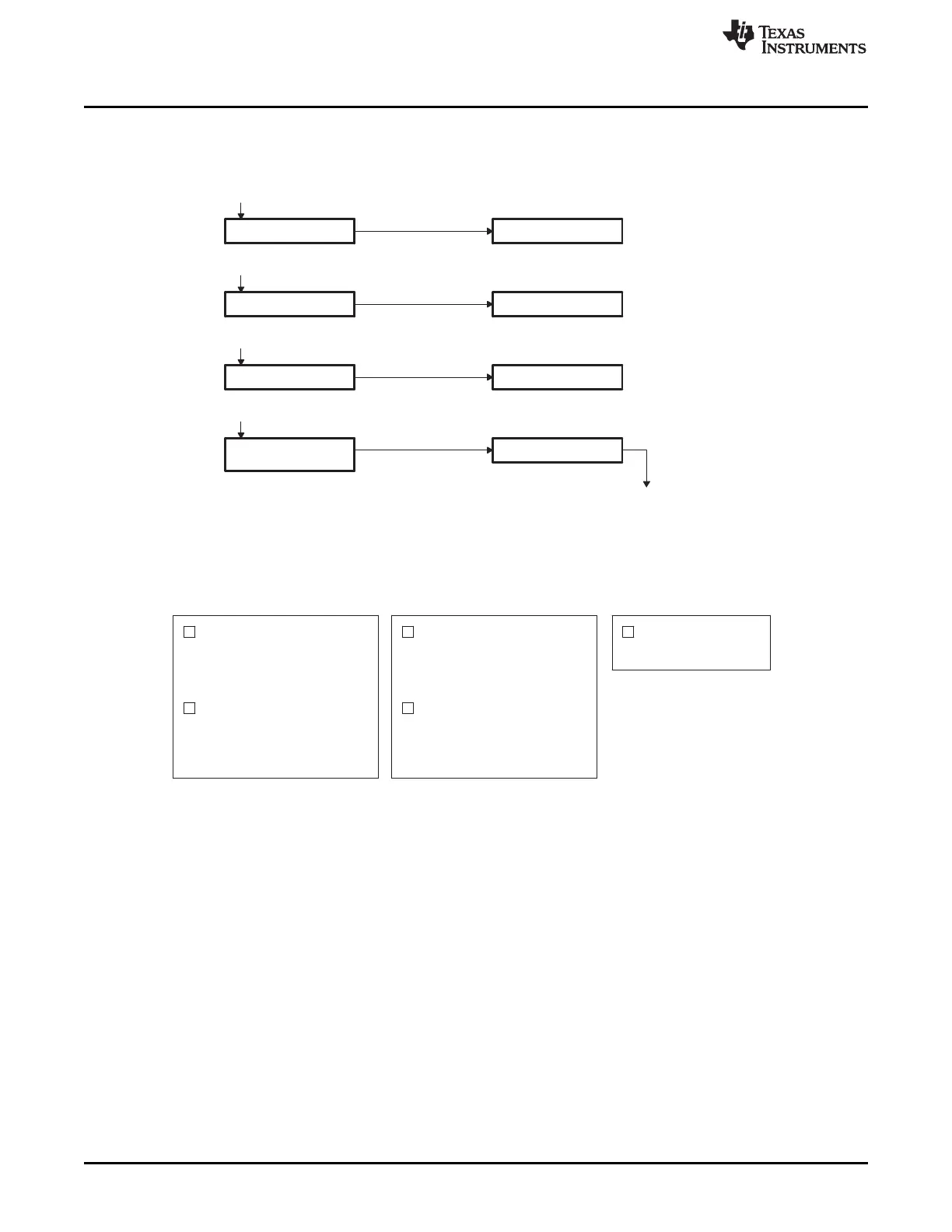

Enable transfer

complete chaining:

OPT.TCCHEN = 1

OPT.TCC = 01000b

Enable intermediate transfer

complete chaining:

OPT.ITCCHEN = 1

OPT.TCC = 01000b

Disable intermediate transfer

OPT.TCINTEN = 1

OPT.ITCCHEN = 0

complete chaining:

OPT.TCC = 01000b

complete chaining:

Enable transfer

Setup

Channel 48 parameters

for chaining for chaining

Channel 8 parameters

Enable channel 48

EER.E48 = 1

Event enable register (EER)

Functional Description

www.ti.com

Figure 11-39. Intermediate Transfer Completion Chaining Example

11.3.19.4.5.2 Breaking Up Large Transfers with Intermediate Chaining

Another feature of intermediate transfer chaining (ITCCHEN) is for breaking up large transfers. A large

transfer may lock out other transfers of the same priority level for the duration of the transfer. For example,

a large transfer on queue 0 from the internal memory to the external memory using the EMIF may starve

other EDMA3 transfers on the same queue. In addition, this large high-priority transfer may prevent the

EMIF for a long duration to service other lower priority transfers. When a large transfer is considered to be

high priority, it should be split into multiple smaller transfers. Figure 11-40 shows the EDMA3 setup and

illustration of an example single large block transfer.

934

Enhanced Direct Memory Access (EDMA) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...