www.ti.com

McSPI Registers

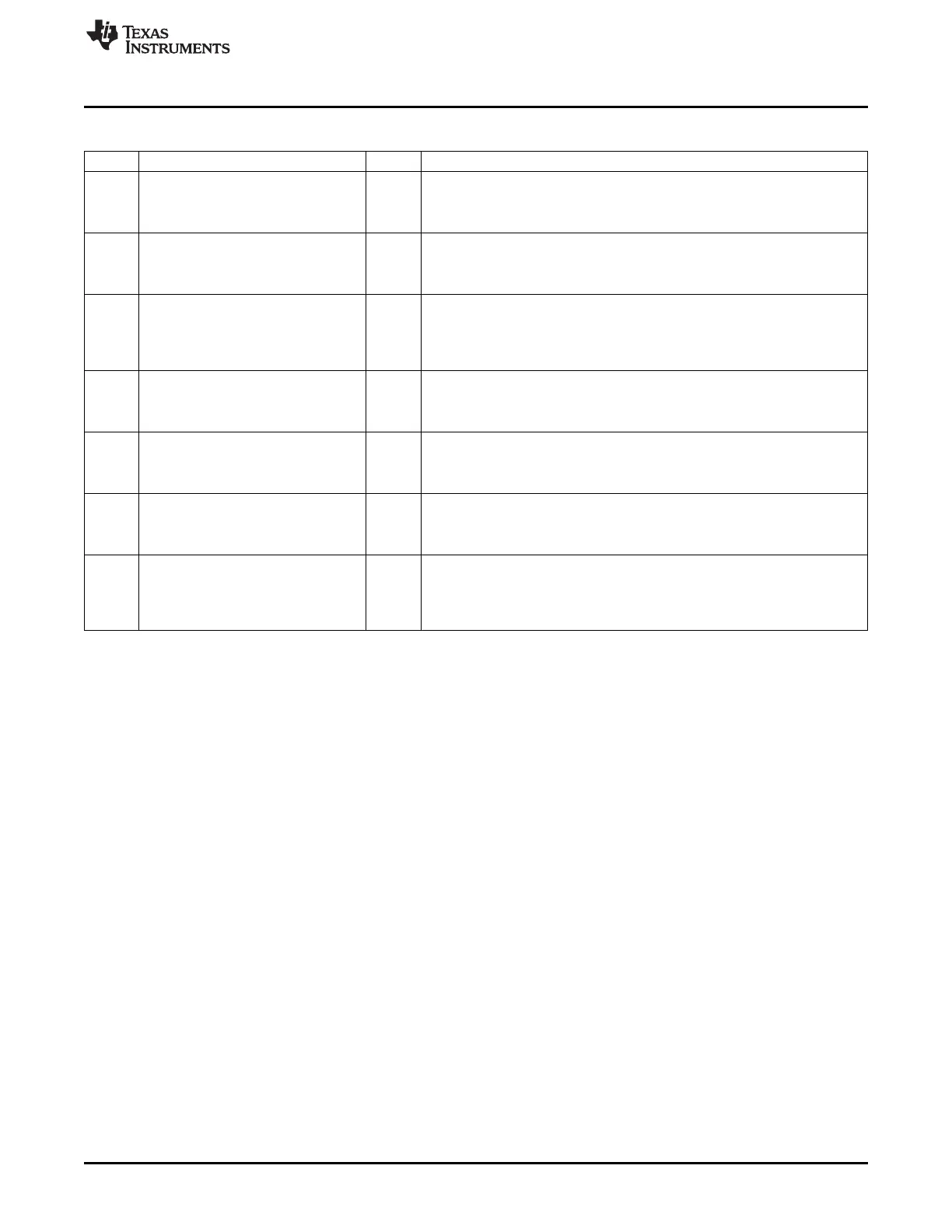

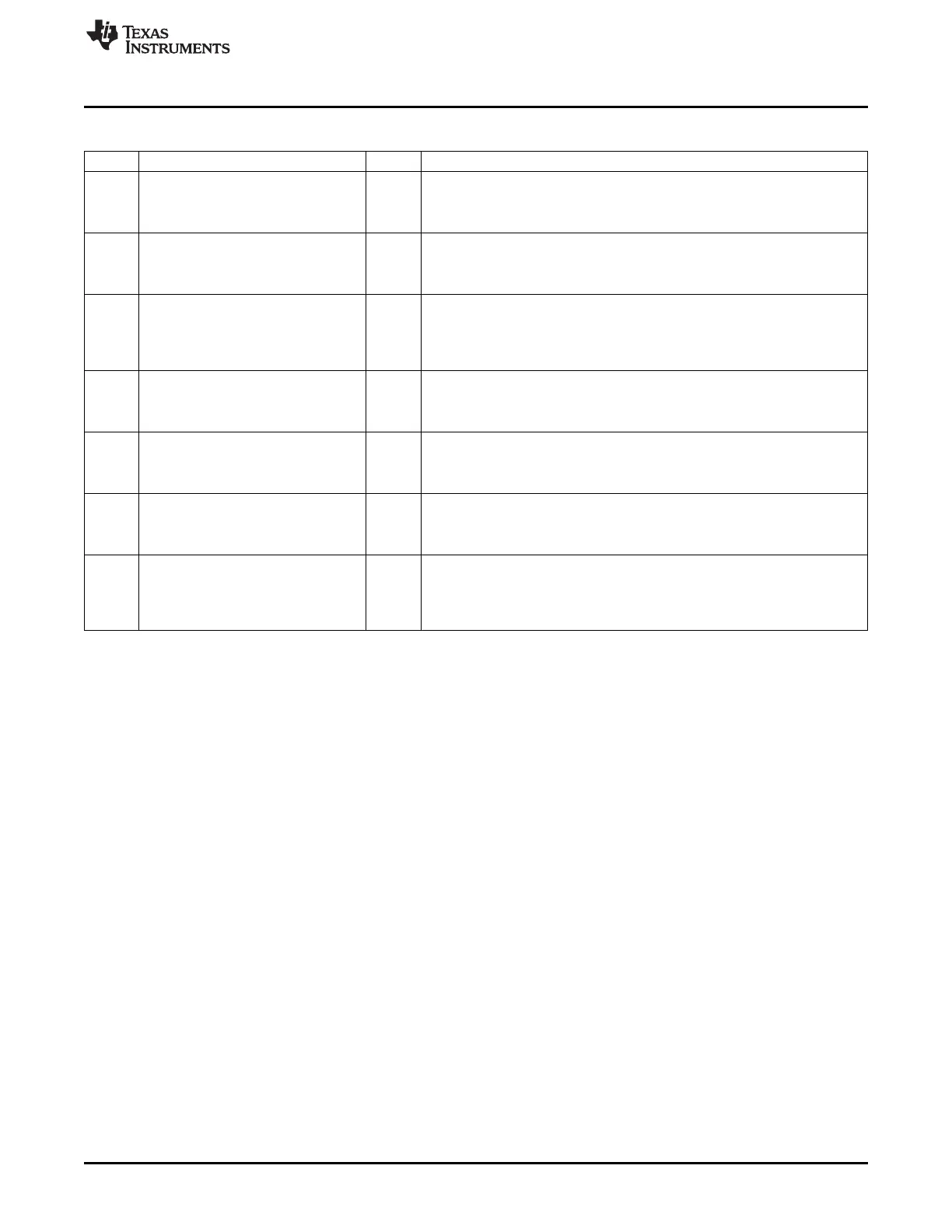

Table 24-15. McSPI Interrupt Enable Register (MCSPI_IRQENABLE) Field Descriptions (continued)

Bit Field Value Description

6 RX1_FULL_ ENABLE MCSPI_RX1 receiver register full or almost full interrupt enable (channel 1)

0 Interrupt is disabled.

1 Interrupt is enabled.

5 TX1_UNDERFLOW_ ENABLE MCSPI_TX1 transmitter register underflow interrupt enable (channel 1).

0 Interrupt is disabled.

1 Interrupt is enabled.

4 TX1_EMPTY_ ENABLE MCSPI_TX1 transmitter register empty or almost empty interrupt enable

(channel 1).

0 Interrupt is disabled.

1 Interrupt is enabled.

3 RX0_OVERFLOW_ ENABLE MCSPI_RX0 receivier register overflow interrupt enable (channel 0).

0 Interrupt is disabled.

1 Interrupt is enabled.

2 RX0_FULL_ ENABLE MCSPI_RX0 receiver register full or almost full interrupt enable (channel 0).

0 Interrupt is disabled.

1 Interrupt is enabled.

1 TX0_UNDERFLOW_ ENABLE MCSPI_TX0 transmitter register underflow interrupt enable (channel 0).

0 Interrupt is disabled.

1 Interrupt is enabled.

0 TX0_EMPTY_ ENABLE MCSPI_TX0 transmitter register empty or almost empty interrupt enable

(channel 0).

0 Interrupt is disabled.

1 Interrupt is enabled.

4041

SPRUH73H–October 2011–Revised April 2013 Multichannel Serial Port Interface (McSPI)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...