www.ti.com

Functional Description

The transfer completion code (TCC) value is directly mapped to the bits of the interrupt pending register

(IPR/IPRH). For example, if TCC = 10 0001b, IPRH[1] is set after transfer completion, and results in

interrupt generation to the CPU(s) if the completion interrupt is enabled for the CPU. See

Section 11.3.9.1.1 for details on enabling EDMA3 transfer completion interrupts.

When a completion code is returned (as a result of early or normal completions), the corresponding bit in

IPR/IPRH is set if transfer completion interrupt (final/intermediate) is enabled in the channel options

parameter (OPT) for a PaRAM set associated with the transfer.

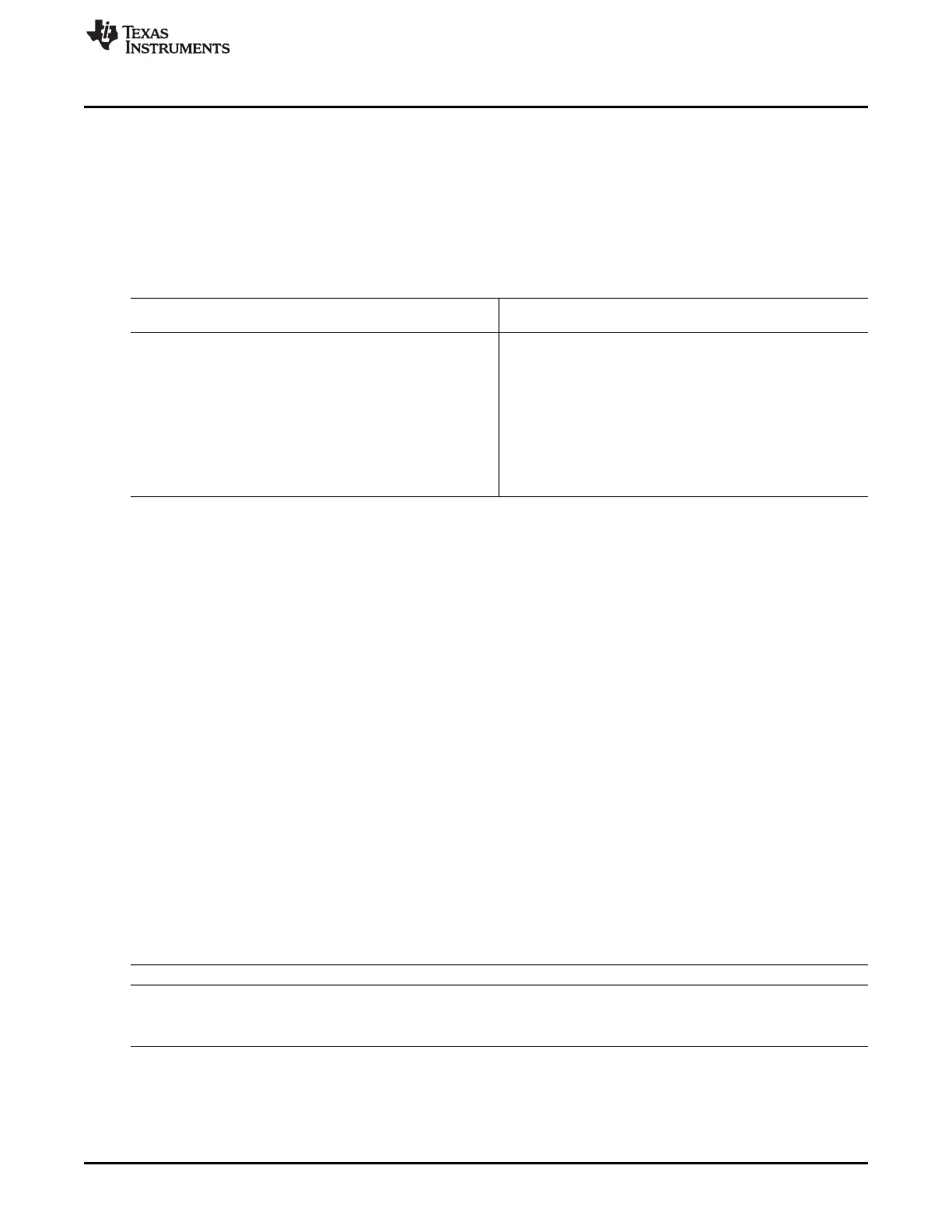

Table 11-15. Transfer Complete Code (TCC) to EDMA3CC Interrupt Mapping

TCC Bits in OPT TCC Bits in OPT

IPR Bit Set IPRH Bit Set

(1)

(TCINTEN/ITCINTEN = 1) (TCINTEN/ITCINTEN = 1)

0 IPR0 20h IPR32/IPRH0

1 IPR1 21h IPR33/IPRH1

2h IPR2 22h IPR34/IPRH2

3h IPR3 23h IPR35/IPRH3

4h IPR4 24h IPR36/IPRH4

... ... ... ...

1Eh IPR30 3Eh IPR62/IPRH30

1Fh IPR31 3Fh IPR63/IPRH31

(1)

Bit fields IPR[32-63] correspond to bits 0 to 31 in IPRH, respectively.

You can program the transfer completion code (TCC) to any value for a DMA/QDMA channel. A direct

relation between the channel number and the transfer completion code value does not need to exist. This

allows multiple channels having the same transfer completion code value to cause a CPU to execute the

same interrupt service routine (ISR) for different channels.

If the channel is used in the context of a shadow region and you intend for the shadow region interrupt to

be asserted, then ensure that the bit corresponding to the TCC code is enabled in IER/IERH and in the

corresponding shadow region's DMA region access registers (DRAE/DRAEH).

You can enable Interrupt generation at either final transfer completion or intermediate transfer completion,

or both. Consider channel m as an example.

• If the final transfer interrupt (TCCINT = 1 in OPT) is enabled, the interrupt occurs after the last transfer

request of channel m is either submitted or completed (depending on early or normal completion).

• If the intermediate transfer interrupt (ITCCINT = 1 in OPT) is enabled, the interrupt occurs after every

transfer request, except the last TR of channel m is either submitted or completed (depending on early

or normal completion).

• If both final and intermediate transfer completion interrupts (TCCINT = 1, and ITCCINT = 1 in OPT) are

enabled, then the interrupt occurs after every transfer request is submitted or completed (depending on

early or normal completion).

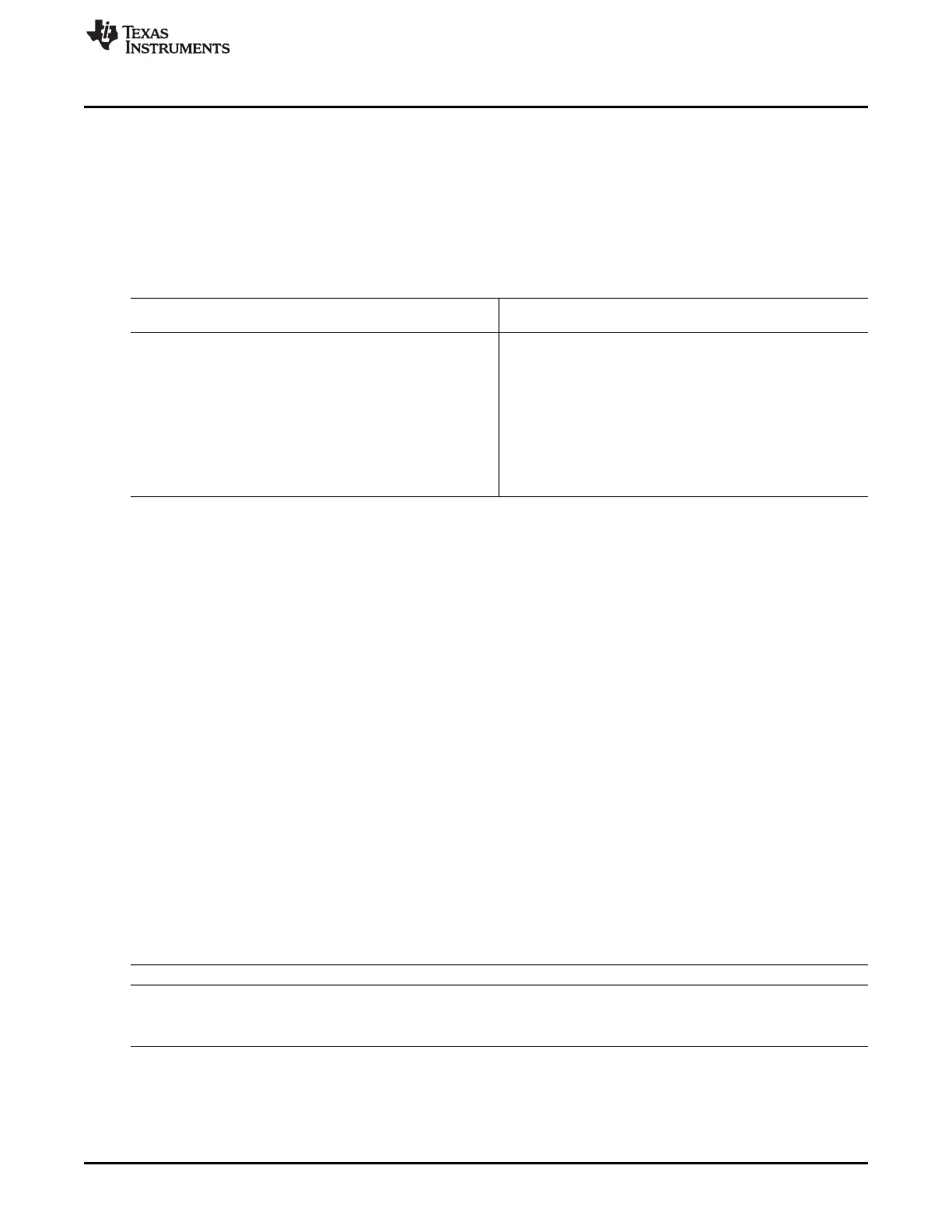

Table 11-16 shows the number of interrupts that occur in different synchronized scenarios. Consider

channel 31, programmed with ACNT = 3, BCNT = 4, CCNT = 5, and TCC = 30.

Table 11-16. Number of Interrupts

Options A-Synchronized AB-Synchronized

TCINTEN = 1, ITCINTEN = 0 1 (Last TR) 1 (Last TR)

TCINTEN = 0, ITCINTEN = 1 19 (All but the last TR) 4 (All but the last TR)

TCINTEN = 1, ITCINTEN = 1 20 (All TRs) 5 (All TRs)

903

SPRUH73H–October 2011–Revised April 2013 Enhanced Direct Memory Access (EDMA)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...