I2C Registers

www.ti.com

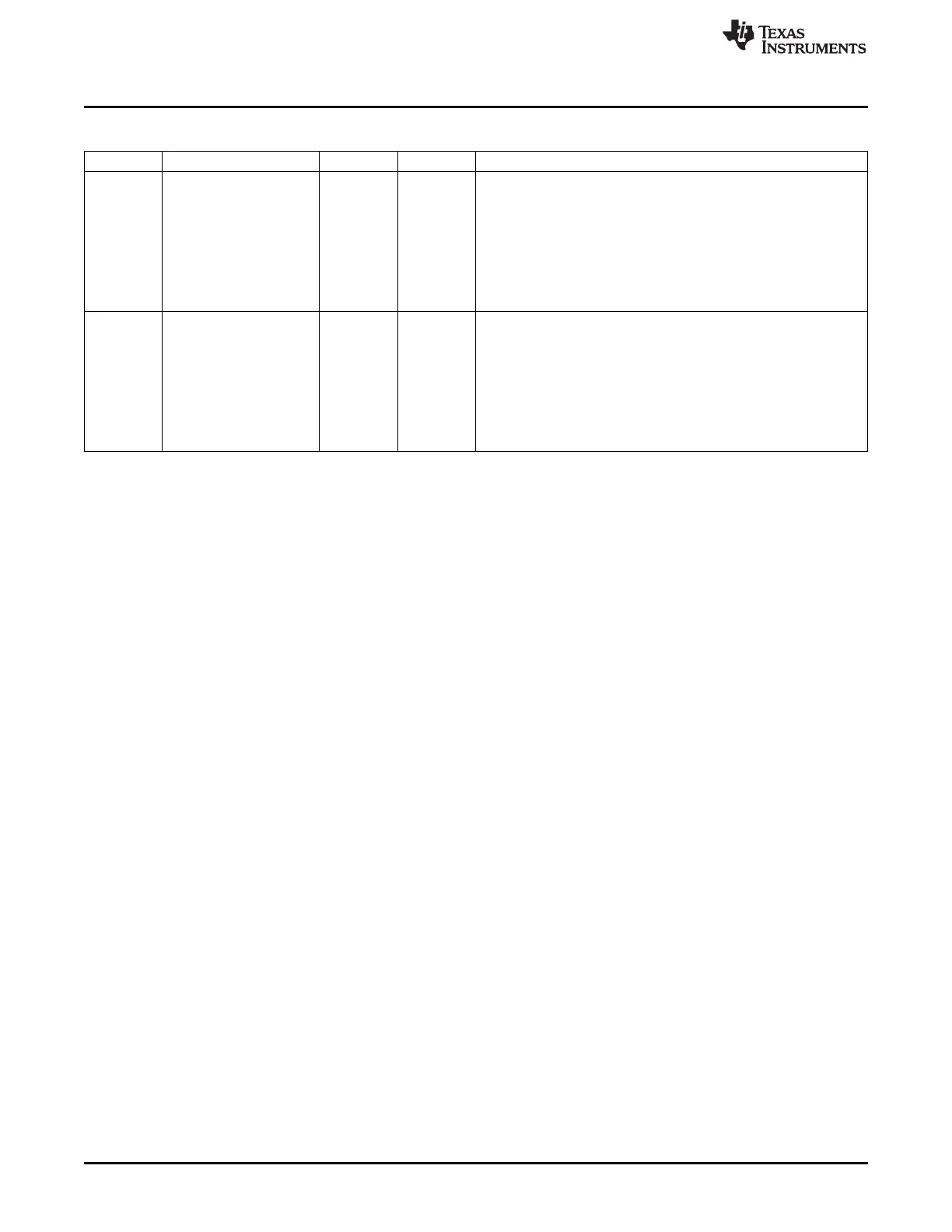

Table 21-11. I2C_SYSC Register Field Descriptions (continued)

Bit Field Type Reset Description

1 SRST R/W 0h SoftReset bit.

When this bit is set to 1, entire module is reset as for the hardware

reset.

This bit is automatically cleared to 0 by the core and it is only reset

by the hardware reset.

During reads, it always returns 0.

Value after reset is low.

0x0 = Normal mode

0x1 = The module is reset

0 AUTOIDLE R/W 0h Autoidle bit.

When this bit is set to 1, the module activates its own idle mode

mechanism.

By evaluating its internal state, the module can decide to gate part of

his internal clock tree in order to improve the overall power

consumption.

Value after reset is high.

0x0 = Auto Idle mechanism is disabled

0x1 = Auto Idle mechanism is enabled

3720

I2C SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...