www.ti.com

Multimedia Card Registers

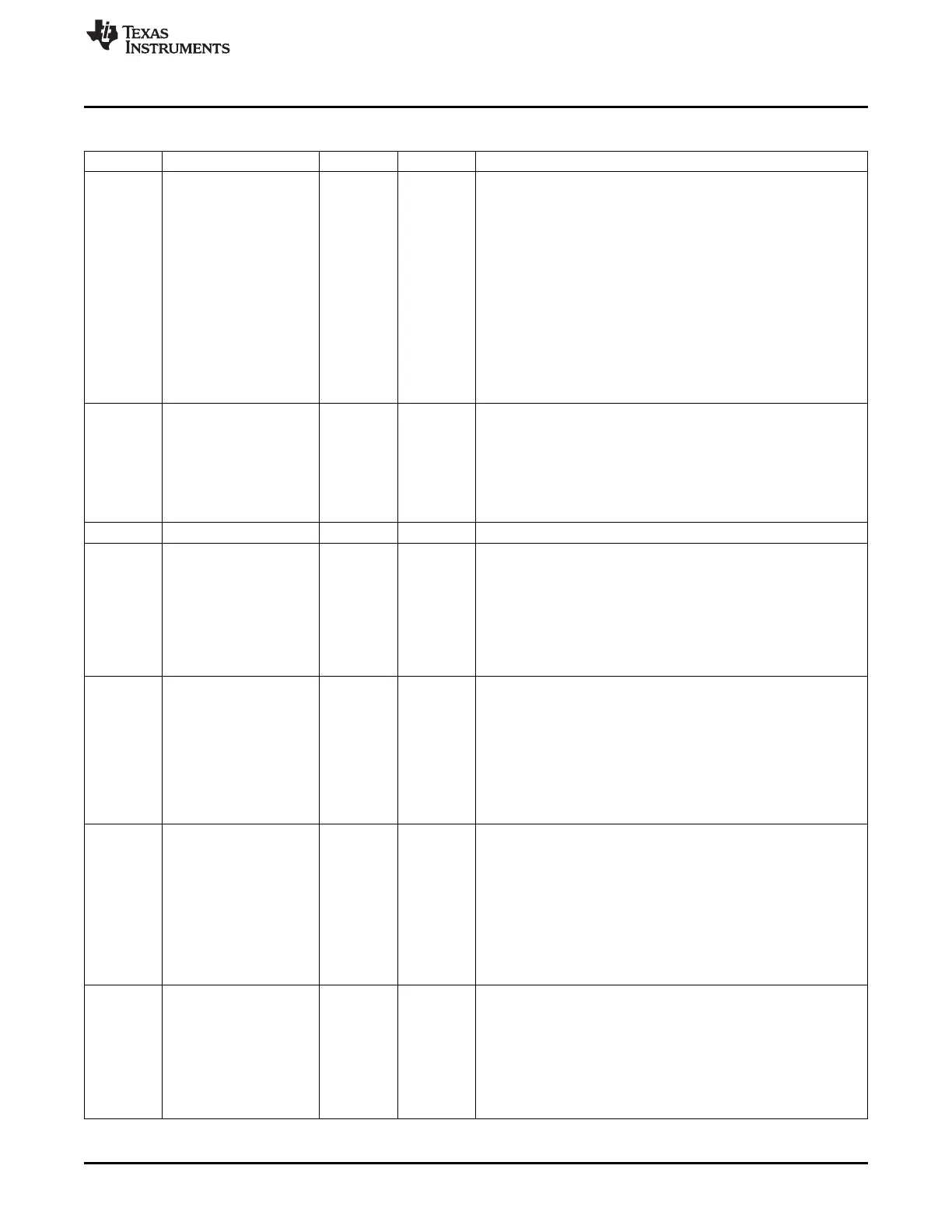

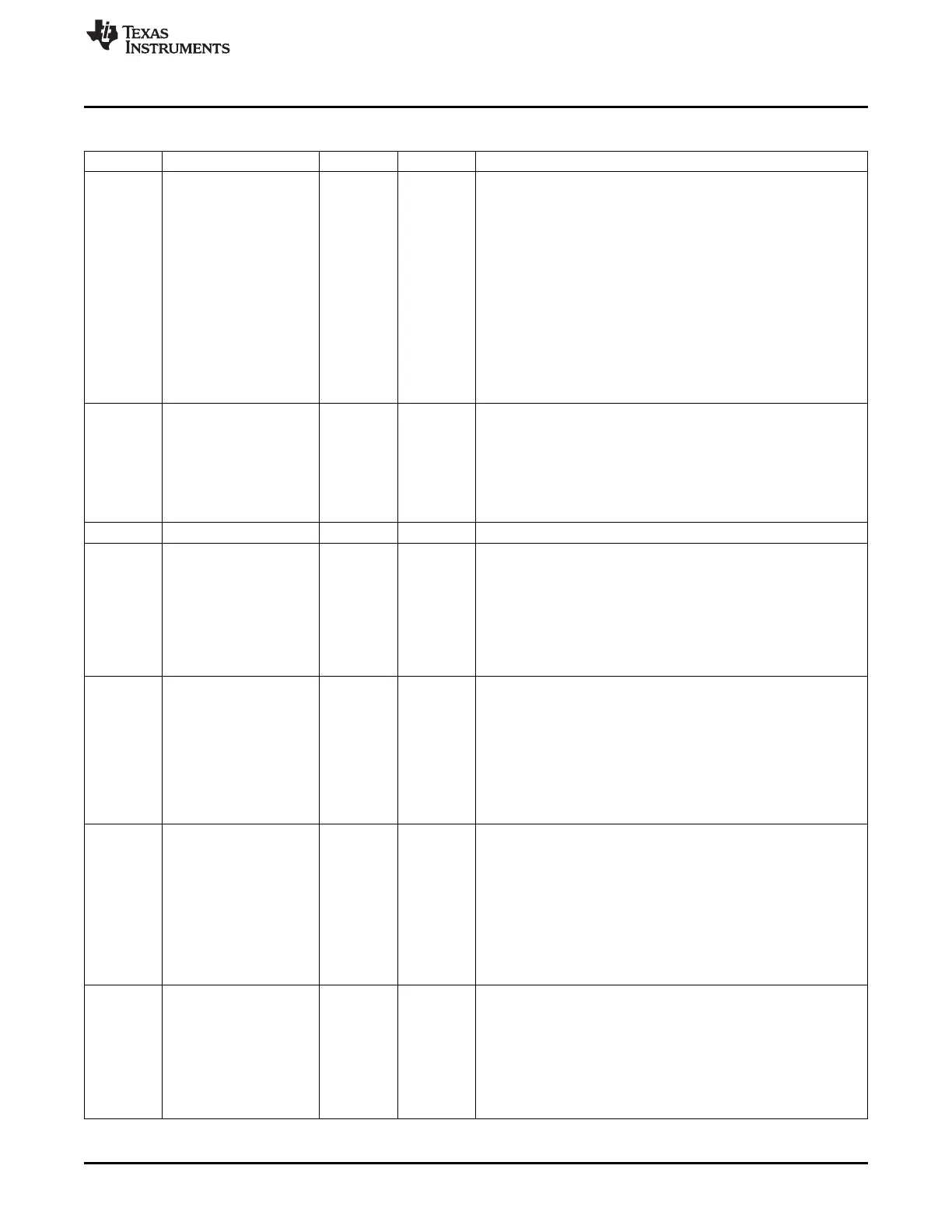

Table 18-38. SD_STAT Register Field Descriptions (continued)

Bit Field Type Reset Description

25 ADMAE R/W 0h ADMA Error.

This bit is set when the Host Controller detects errors during ADMA

based data transfer.

The state of the ADMA at an error occurrence is saved in the ADMA

Error Status Register.

In addition, the Host Controller generates this interrupt when it

detects invalid descriptor data (Valid=0) at the ST_FDS state.

ADMA Error State in the ADMA Error Status indicates that an error

occurs in ST_FDS state.

The Host Driver may find that Valid bit is not set at the error

descriptor.

0x0(W) = Status bit unchanged

0x0(R) = No interrupt

0x1(W) = Status is cleared.

0x1(R) = ADMA error

24 ACE R/W 0h Auto CMD12 error.

This bit is set automatically when one of the bits in Auto CMD12

Error status register has changed from 0 to 1.

0x0(W) = Status bit unchanged

0x0(R) = No error

0x1(W) = Status is cleared.

0x1(R) = AutoCMD12 error

23 Reserved R 0h

22 DEB R/W 0h Data End Bit error.

This bit is set automatically when detecting a 0 at the end bit position

of read data on mmc_dat line or at the end position of the CRC

status in write mode.

0x0(W) = Status bit unchanged

0x0(R) = No error

0x1(W) = Status is cleared.

0x1(R) = Data end bit error

21 DCRC R/W 0h Data CRC Error.

This bit is set automatically when there is a CRC16 error in the data

phase response following a block read command or if there is a

3-bit CRC status different of a position "010" token during a block

write command.

0x0(W) = Status bit unchanged

0x0(R) = No error

0x1(W) = Status is cleared.

0x1(R) = Data CRC error

20 DTO R/W 0h Data timeout error.

This bit is set automatically according to the following conditions:

Busy timeout for R1b, R5b response type.

Busy timeout after write CRC status.

Write CRC status timeout.

Read data timeout.

0x0(W) = Status bit unchanged

0x0(R) = No error

0x1(W) = Status is cleared.

0x1(R) = Time out

19 CIE R/W 0h Command index error.

This bit is set automatically when response index differs from

corresponding command index previously emitted.

It depends on the enable bit (SD_CMD[20] CICE).

0x0(W) = Status bit unchanged

0x0(R) = No error

0x1(W) = Status is cleared.

0x1(R) = Command index error

3425

SPRUH73H–October 2011–Revised April 2013 Multimedia Card (MMC)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...