www.ti.com

GPMC

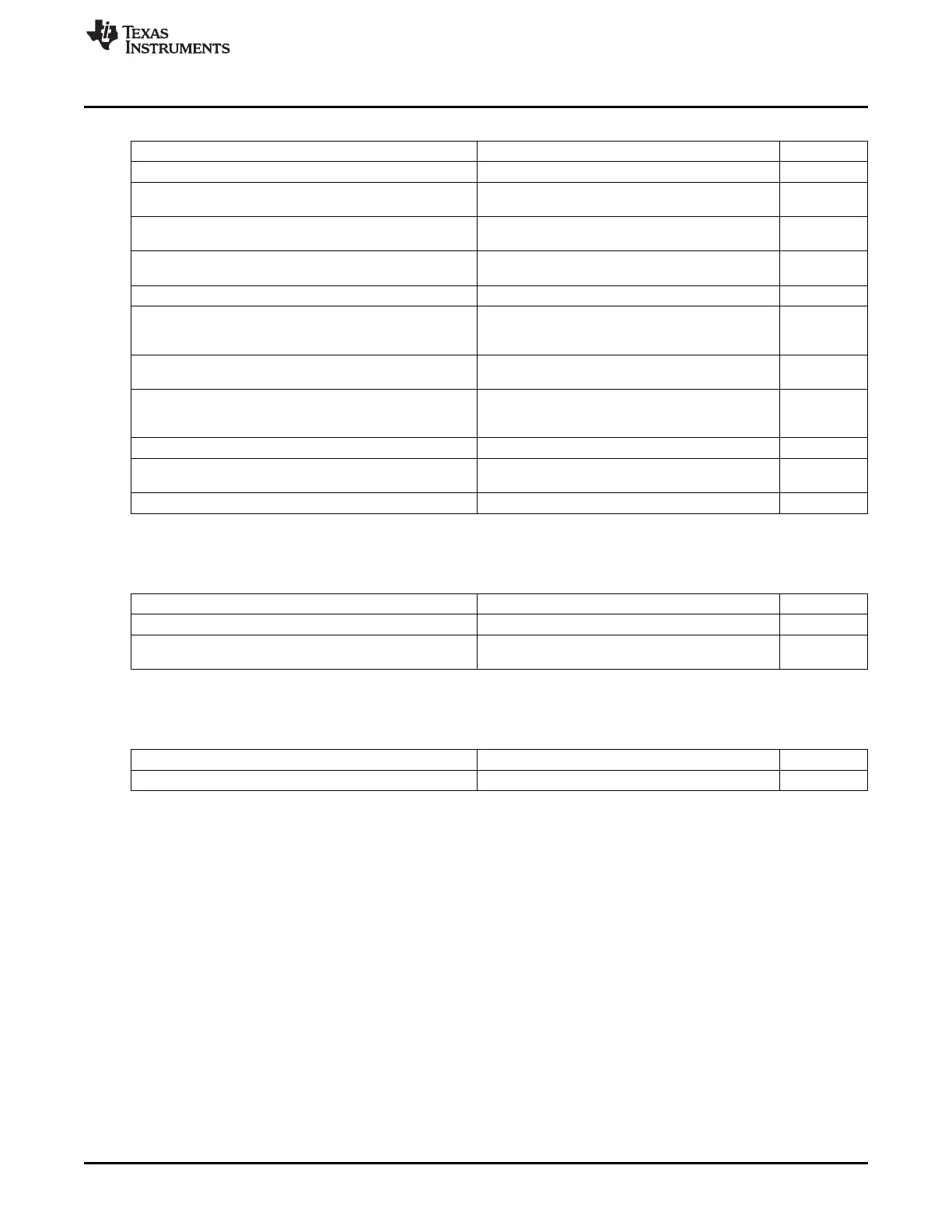

Table 7-36. Prefetch and Write-Posting Engine

Sub-process Name Register / Bitfield Value

Disable the engine before configuration GPMC_PREFETCH_CONTROL[0] STARTENGINE 0

Select the chip-select associated with a NAND device where GPMC_PREFETCH_CONFIG1[26-24]

x

the prefetch engine is active ENGINECSSELECTOR

Select access direction through prefetch engine, read or

GPMC_PREFETCH_CONFIG1[0] ACCESSMODE x

write.

GPMC_PREFETCH_CONFIG1[14-8]

Select the threshold used to issue a DMA request x

FIFOTHRESHOLD

Select either DMA synchronized mode or SW manual mode. GPMC_PREFETCH_CONFIG1[2] DMAMODE x

Select if the engine immediately starts accessing the

memory upon STARTENGINE assertion or if hardware GPMC_PREFETCH_CONFIG1[3] SYNCHROMODE x

synchronization based on a WAIT signal is used.

Select which wait pin edge detector should start the engine GPMC_PREFETCH_CONFIG1[5-4]

x

in synchronized mode WAITPINSELECTOR

Enter a number of clock cycles removed to timing

GPMC_PREFETCH_CONFIG1[30-28]

parameters (For all back-to-back accesses to the NAND x

CYCLEOPTIMIZATION

flash but not the first one)

Enable the prefetch postwite engine GPMC_PREFETCH_CONFIG1[7] ENABLEENGINE 1

Select the number of bytes to be read or written by the GPMC_PREFETCH_CONFIG2[13-0]

x

engine to the selected chip-select TRANSFERCOUNT

Start the prefetch engine GPMC_PREFETCH_CONTROL[0] STARTENGINE 1

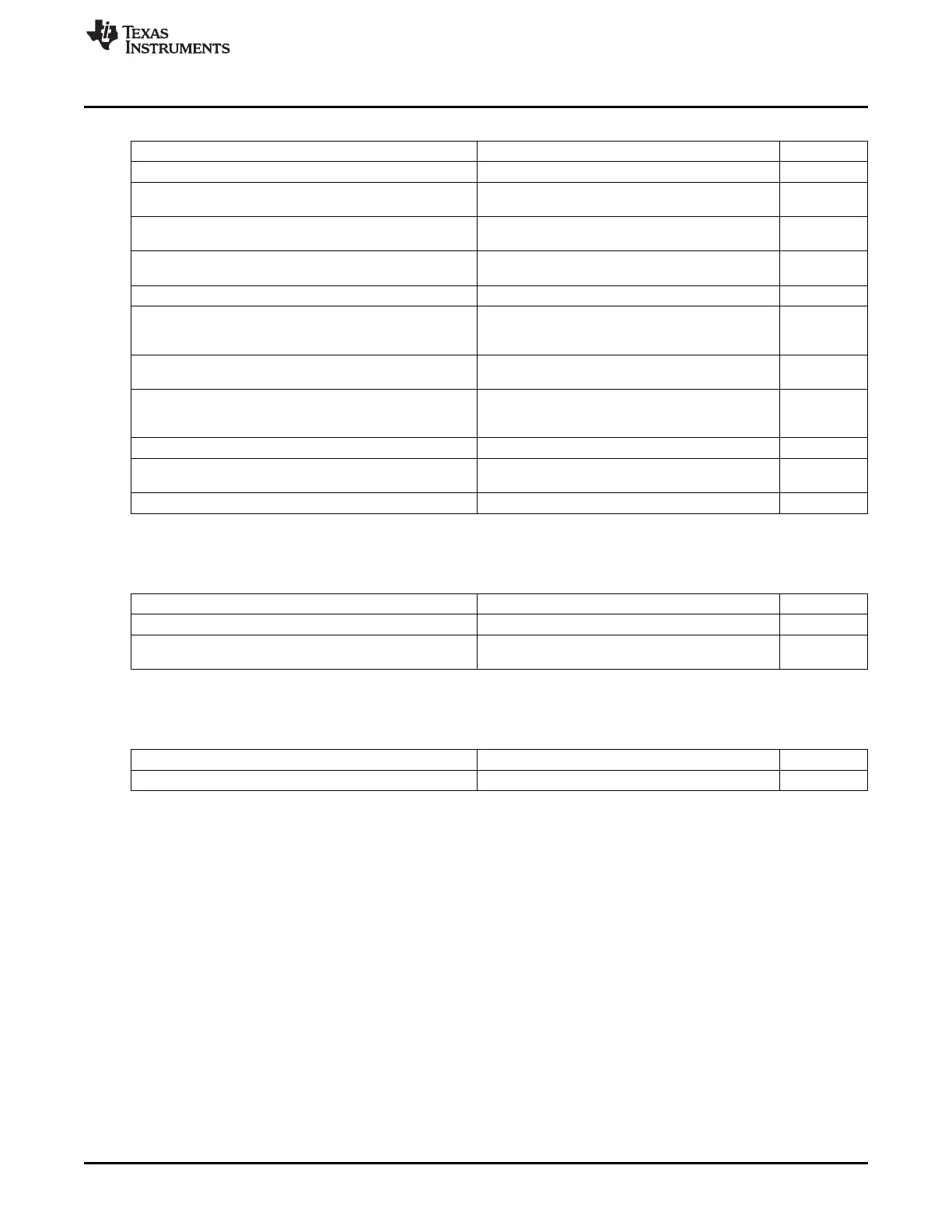

Table 7-37. WAIT Pin Configuration

Sub-process Name Register / Bitfield Value

Selects when the engine starts the access to CS GPMC_PREFETCH_CONFIG1[3] SYNCHROMODE x

Select which wait pin edge detector should start the engine GPMC_PREFETCH_CONFIG1[5-4]

x

in synchronized mode WAITPINSELECTOR

Table 7-38. Enable Chip-Select

Sub-process Name Register / Bitfield Value

When all parameters are configured, enable the chip-select GPMC_CONFIG7_i[6] CSVALID x

341

SPRUH73H–October 2011–Revised April 2013 Memory Subsystem

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...