Ethernet Subsystem Registers

www.ti.com

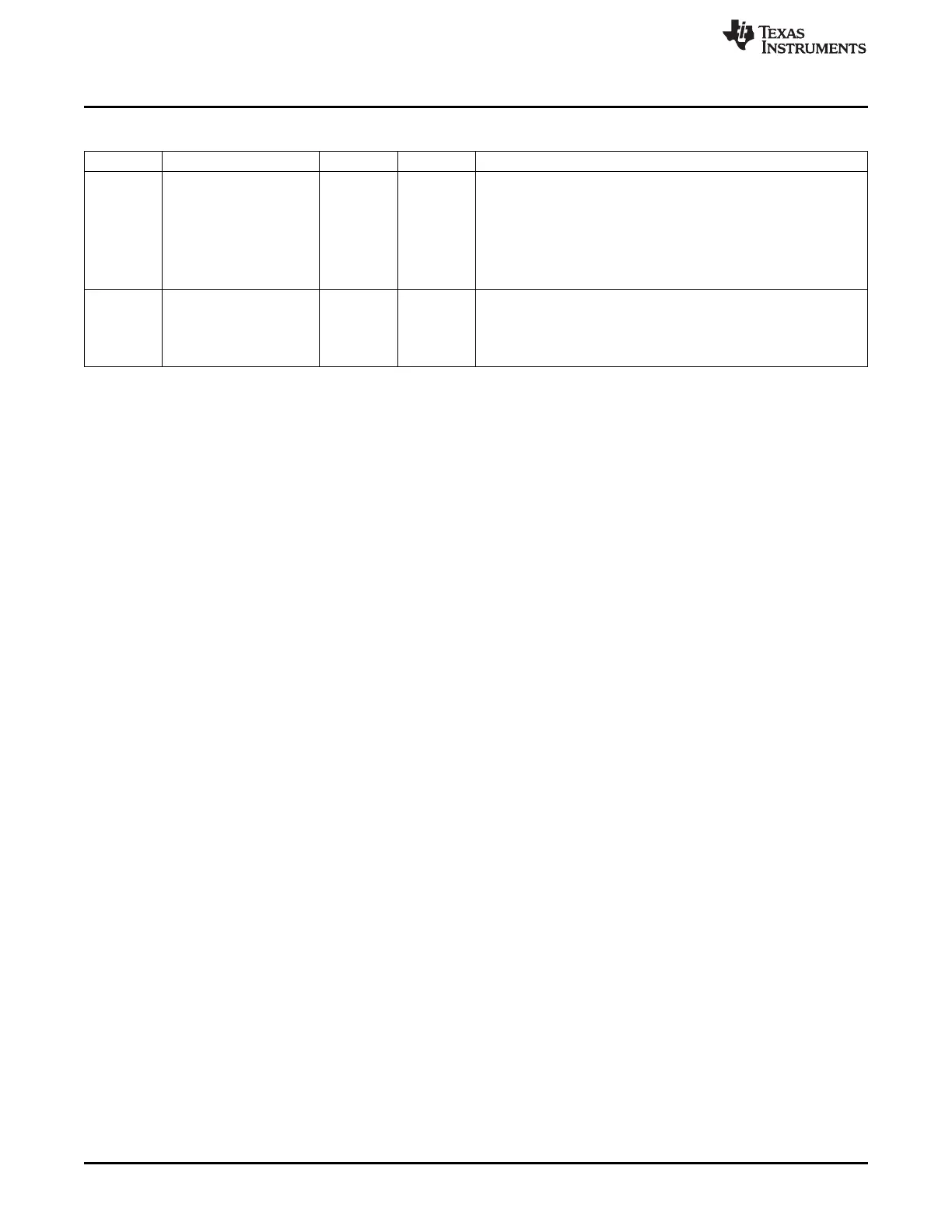

Table 14-47. DMACONTROL Register Field Descriptions (continued)

Bit Field Type Reset Description

1 RX_OWNERSHIP R/W 0h Receive Ownership Write Bit Value.

0 - The CPDMA writes the receive ownership bit to zero at the end

of packet processing as specified in CPPI 3.0.

1 - The CPDMA writes the receive ownership bit to one at the end of

packet processing.

Users who do not use the ownership mechanism can use this mode

to preclude the necessity of software having to set this bit each time

the buffer descriptor is used.

0 TX_PTYPE R/W 0h Transmit Queue Priority Type

0 - The queue uses a round robin scheme to select the next channel

for transmission.

1 - The queue uses a fixed (channel 7 highest priority) priority

scheme to select the next channel for transmission

1266

Ethernet Subsystem SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...