Ethernet Subsystem Registers

www.ti.com

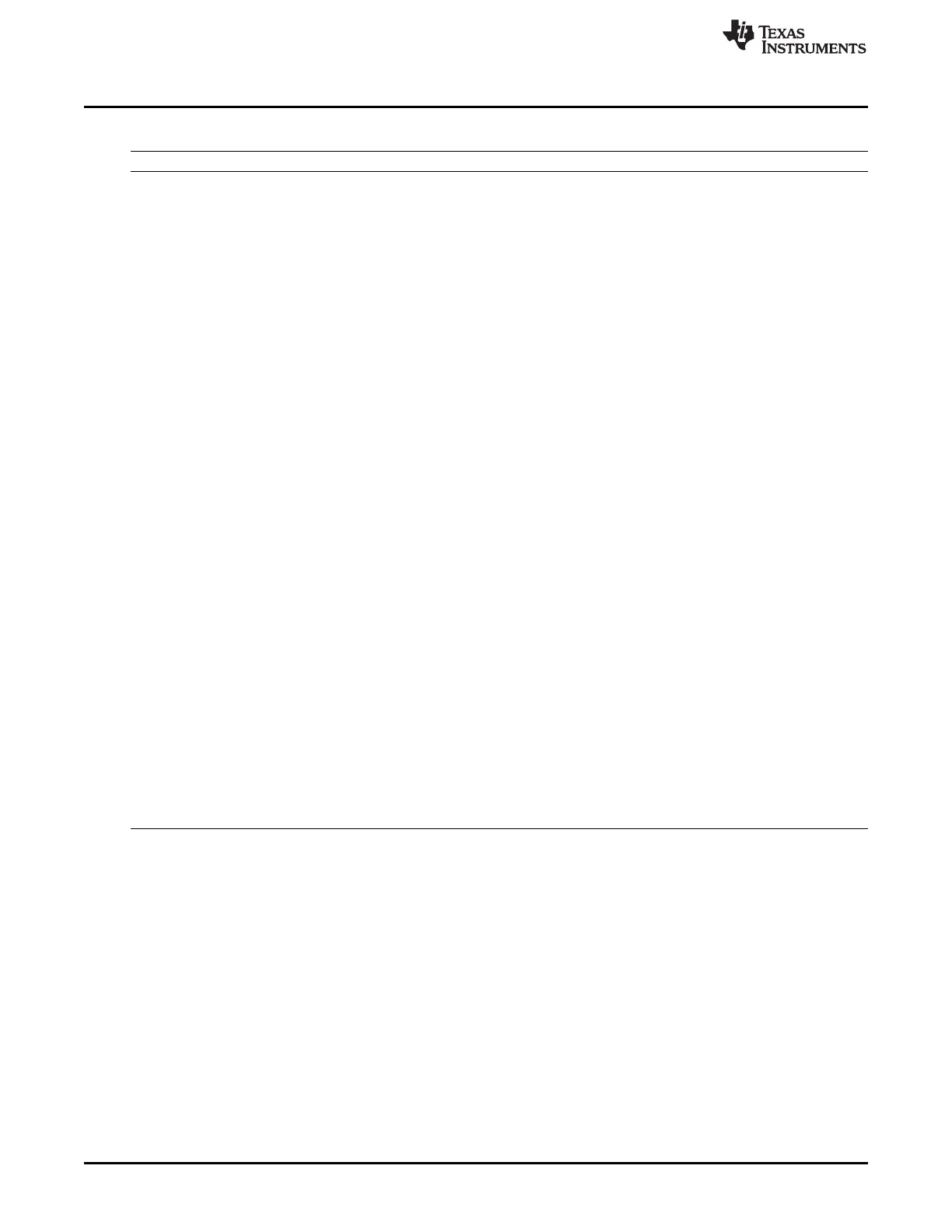

Table 14-135. CPSW_PORT REGISTERS (continued)

Offset Acronym Register Name Section

114h P1_PORT_VLAN Section 14.5.6.21

118h P1_TX_PRI_MAP Section 14.5.6.22

11Ch P1_TS_SEQ_MTYPE Section 14.5.6.23

120h P1_SA_LO Section 14.5.6.24

124h P1_SA_HI Section 14.5.6.25

128h P1_SEND_PERCENT Section 14.5.6.26

130h P1_RX_DSCP_PRI_MAP0 Section 14.5.6.27

134h P1_RX_DSCP_PRI_MAP1 Section 14.5.6.28

138h P1_RX_DSCP_PRI_MAP2 Section 14.5.6.29

13Ch P1_RX_DSCP_PRI_MAP3 Section 14.5.6.30

140h P1_RX_DSCP_PRI_MAP4 Section 14.5.6.31

144h P1_RX_DSCP_PRI_MAP5 Section 14.5.6.32

148h P1_RX_DSCP_PRI_MAP6 Section 14.5.6.33

14Ch P1_RX_DSCP_PRI_MAP7 Section 14.5.6.34

200h P2_CONTROL Section 14.5.6.35

208h P2_MAX_BLKS Section 14.5.6.36

20Ch P2_BLK_CNT Section 14.5.6.37

210h P2_TX_IN_CTL Section 14.5.6.38

214h P2_PORT_VLAN Section 14.5.6.39

218h P2_TX_PRI_MAP Section 14.5.6.40

21Ch P2_TS_SEQ_MTYPE Section 14.5.6.41

220h P2_SA_LO Section 14.5.6.42

224h P2_SA_HI Section 14.5.6.43

228h P2_SEND_PERCENT Section 14.5.6.44

230h P2_RX_DSCP_PRI_MAP0 Section 14.5.6.45

234h P2_RX_DSCP_PRI_MAP1 Section 14.5.6.46

238h P2_RX_DSCP_PRI_MAP2 Section 14.5.6.47

23Ch P2_RX_DSCP_PRI_MAP3 Section 14.5.6.48

240h P2_RX_DSCP_PRI_MAP4 Section 14.5.6.49

244h P2_RX_DSCP_PRI_MAP5 Section 14.5.6.50

248h P2_RX_DSCP_PRI_MAP6 Section 14.5.6.51

24Ch P2_RX_DSCP_PRI_MAP7 Section 14.5.6.52

1356

Ethernet Subsystem SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...