www.ti.com

Ethernet Subsystem Registers

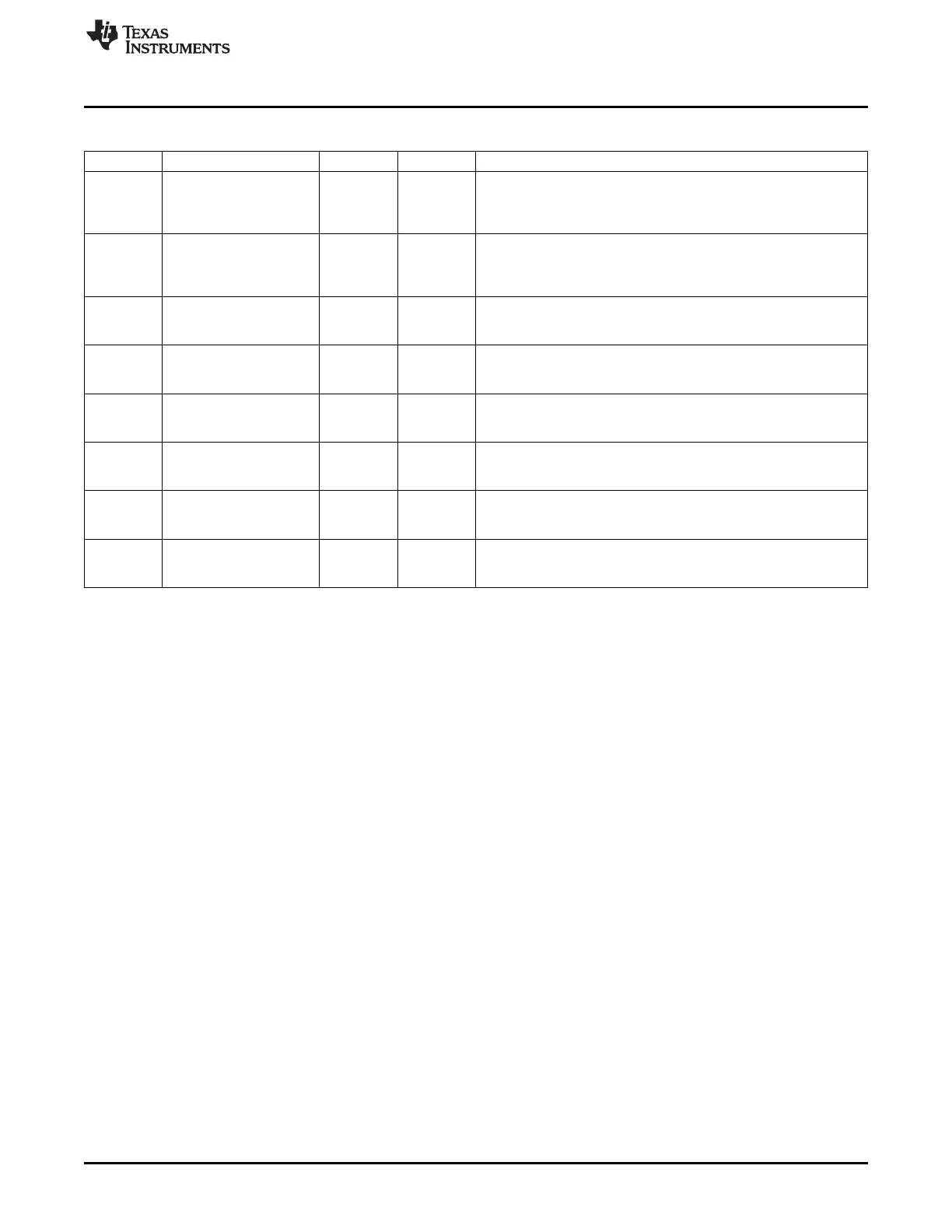

Table 14-170. P2_CONTROL Register Field Descriptions (continued)

Bit Field Type Reset Description

10 P2_TS_130 R/W 0h Port 2 Time Sync Destination IP Address 130 enable

0 - disabled

1 - Annex D (UDP/IPv4) time sync packet destination IP address

number 130 (decimal) is enabled.

9 P2_TS_129 R/W 0h Port 2 Time Sync Destination IP Address 129 enable

0 - disabled

1 - Annex D (UDP/IPv4) time sync packet destination IP address

number 129 (decimal) is enabled.

8 P2_TS_TTL_NONZERO R/W 0h Port 2 Time Sync Time To Live Non-zero enable.

0 = TTL must be zero.

1 = TTL may be any value.

4 P2_TS_ANNEX_D_EN R/W 0h Port 2 Time Sync Annex D enable

0 - Annex D disabled

1 - Annex D enabled

3 P2_TS_LTYPE2_EN R 0h Port 2 Time Sync LTYPE 2 enable

0 - disabled

1 - enabled

2 P2_TS_LTYPE1_EN R/W 0h Port 2 Time Sync LTYPE 1 enable

0 - disabled

1 - enabled

1 P2_TS_TX_EN R/W 0h Port 2 Time Sync Transmit Enable

0 - disabled

1 - enabled

0 P2_TS_RX_EN R/W 0h Port 2 Time Sync Receive Enable

0 - Port 1 Receive Time Sync disabled

1 - Port 1 Receive Time Sync enabled

1393

SPRUH73H–October 2011–Revised April 2013 Ethernet Subsystem

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...