www.ti.com

ARM Cortex-A8 Interrupts

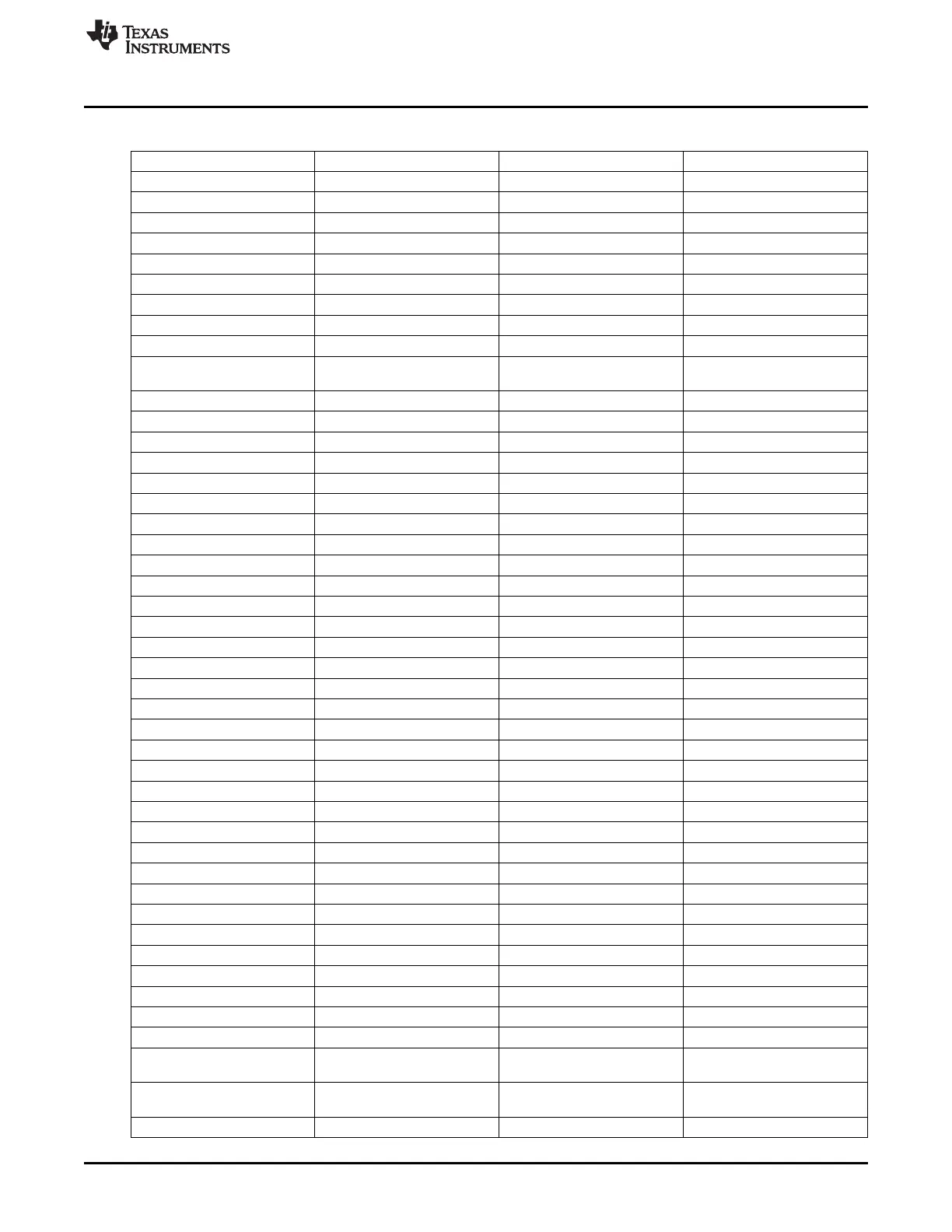

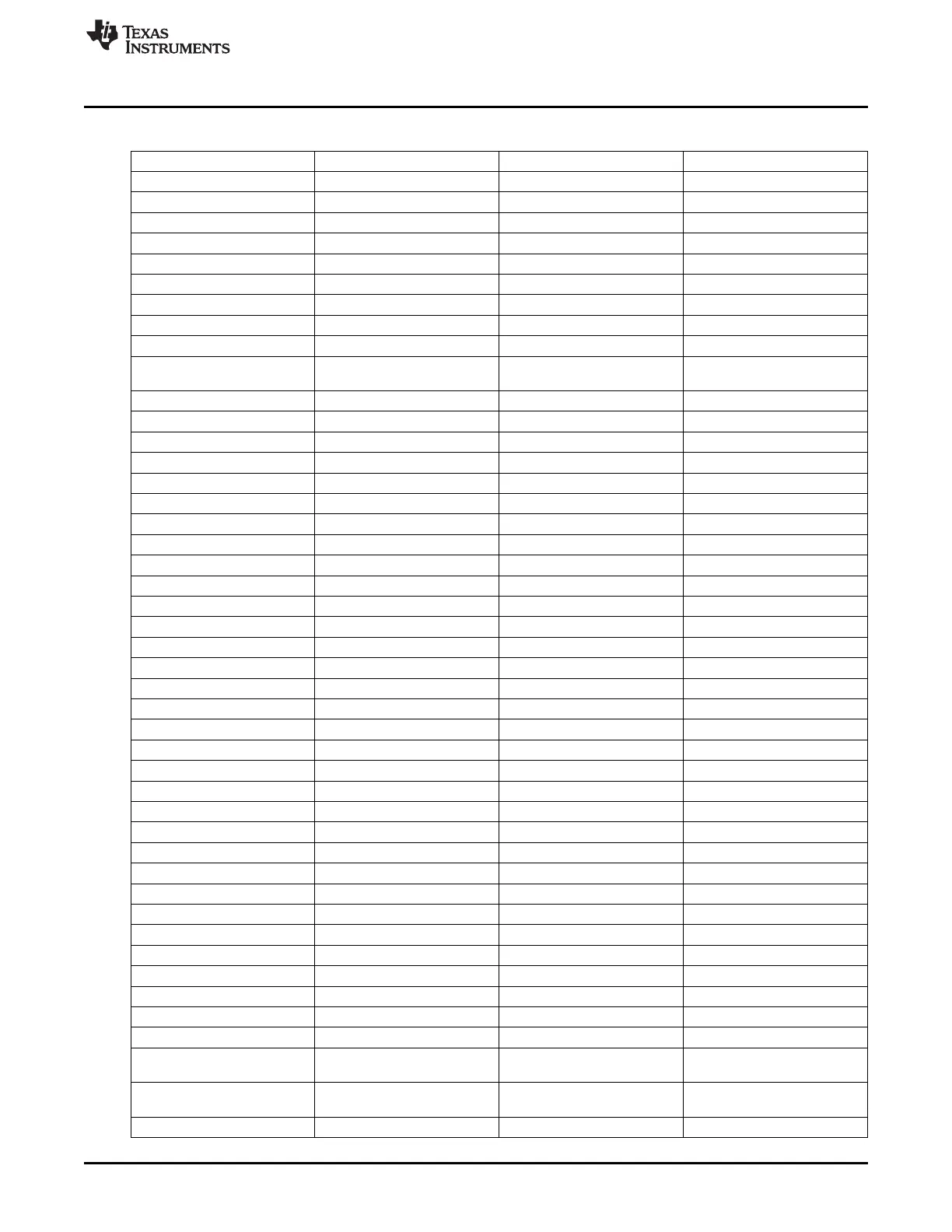

Table 6-1. ARM Cortex-A8 Interrupts (continued)

Int Number Acronym/name Source Signal Name

81 MCARXINT0 McASP0 mcasp_r_intr_pend

82 MCATXINT1 McASP1 mcasp_x_intr_pend

83 MCARXINT1 McASP1 mcasp_r_intr_pend

84 Reserved

85 Reserved

86 ePWM0INT eHRPWM0 (PWM Subsystem) epwm_intr_intr_pend

87 ePWM1INT eHRPWM1 (PWM Subsystem) epwm_intr_intr_pend

88 eQEP1INT eQEP1 (PWM Subsystem) eqep_intr_intr_pend

89 eQEP2INT eQEP2 (PWM Subsystem) eqep_intr_intr_pend

90 DMA_INTR_PIN2 External DMA/Interrupt Pin2 pi_x_dma_event_intr2

(xdma_event_intr2)

91 WDT1INT (Public Watchdog) WDTIMER1 PO_INT_PEND

92 TINT4 DMTIMER4 POINTR_PEND

93 TINT5 DMTIMER5 POINTR_PEND

94 TINT6 DMTIMER6 POINTR_PEND

95 TINT7 DMTIMER7 POINTR_PEND

96 GPIOINT0A GPIO 0 POINTRPEND1

97 GPIOINT0B GPIO 0 POINTRPEND2

98 GPIOINT1A GPIO 1 POINTRPEND1

99 GPIOINT1B GPIO 1 POINTRPEND2

100 GPMCINT GPMC gpmc_sinterrupt

101 DDRERR0 EMIF sys_err_intr_pend

102 Reserved

103 Reserved

104 Reserved

105 Reserved

106 Reserved

107 Reserved

108 Reserved

109 Reserved

110 Reserved

111 Reserved

112 TCERRINT0 TPTC0 tptc_erint_pend_po

113 TCERRINT1 TPTC1 tptc_erint_pend_po

114 TCERRINT2 TPTC2 tptc_erint_pend_po

115 ADC_TSC_PENINT ADC_TSC pen_intr_pend

116 Reserved

117 Reserved

118 Reserved

119 Reserved

120 SMRFLX_MPU subsystem Smart Reflex 0 intrpend

121 SMRFLX_Core Smart Reflex 1 intrpend

122 Reserved

123 DMA_INTR_PIN0 External DMA/Interrupt Pin0 pi_x_dma_event_intr0

(xdma_event_intr0)

124 DMA_INTR_PIN1 External DMA/Interrupt Pin1 pi_x_dma_event_intr1

(xdma_event_intr1)

125 McSPI1INT McSPI1 SINTERRUPTN

201

SPRUH73H–October 2011–Revised April 2013 Interrupts

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...