www.ti.com

GPMC

7.1.3.3.12.4.4 Write-Posting Mode

The write-posting mode is selected when the GPMC_PREFETCH_CONFIG1[0] ACCESSMODE bit is set.

The MPU NAND software driver must issue the correct address pointer initialization command (page

program) before the engine can start writing data into the NAND memory device. The engine starts when

the GPMC_PREFETCH_CONTROL[0] STARTENGINE bit is set to 1. The STARTENGINE bit clears

automatically when posting completes. When all data have been written to the NAND memory device, the

MPU NAND software driver must issue the second cycle program command and monitor the status for

programming process completion (adding ECC handling, if required).

If used, the ECC calculator engine must be started (configured, reset, and enabled) before the posting

engine is started so that the ECC parities are properly calculated on all data written by the prefetch engine

to the associated chip-select.

In write-posting mode, the GPMC_PREFETCH_CONFIG1[3] SYNCHROMODE bit must be cleared so that

posting starts as soon as the STARTENGINE bit is set and the FIFO is not empty.

If the STARTENGINE bit is set after the NAND address phase (page program command), the

STARTENGINE setting is effective only after the actual NAND command completion. To prevent GPMC

stall during this NAND command phase, set the STARTENGINE bit field before the NAND address

completion and ensure that the associated DMA channel is enabled after the NAND address phase.

The posting engine issues a write request when valid data are available from the FIFO and until the

programmed GPMC_PREFETCH_CONFIG2[13-0] TRANSFERCOUNT accesses have been completed.

The STARTENGINE bit clears automatically when posting completes. When all data have been written to

the NAND memory device, the MPU NAND software driver must issue the second cycle program

command and monitor the status for programming process completion. The closing program command

phase must only be issued when the full NAND page has been written into the NAND flash write buffer,

including the spare area data and the ECC parities, if used.

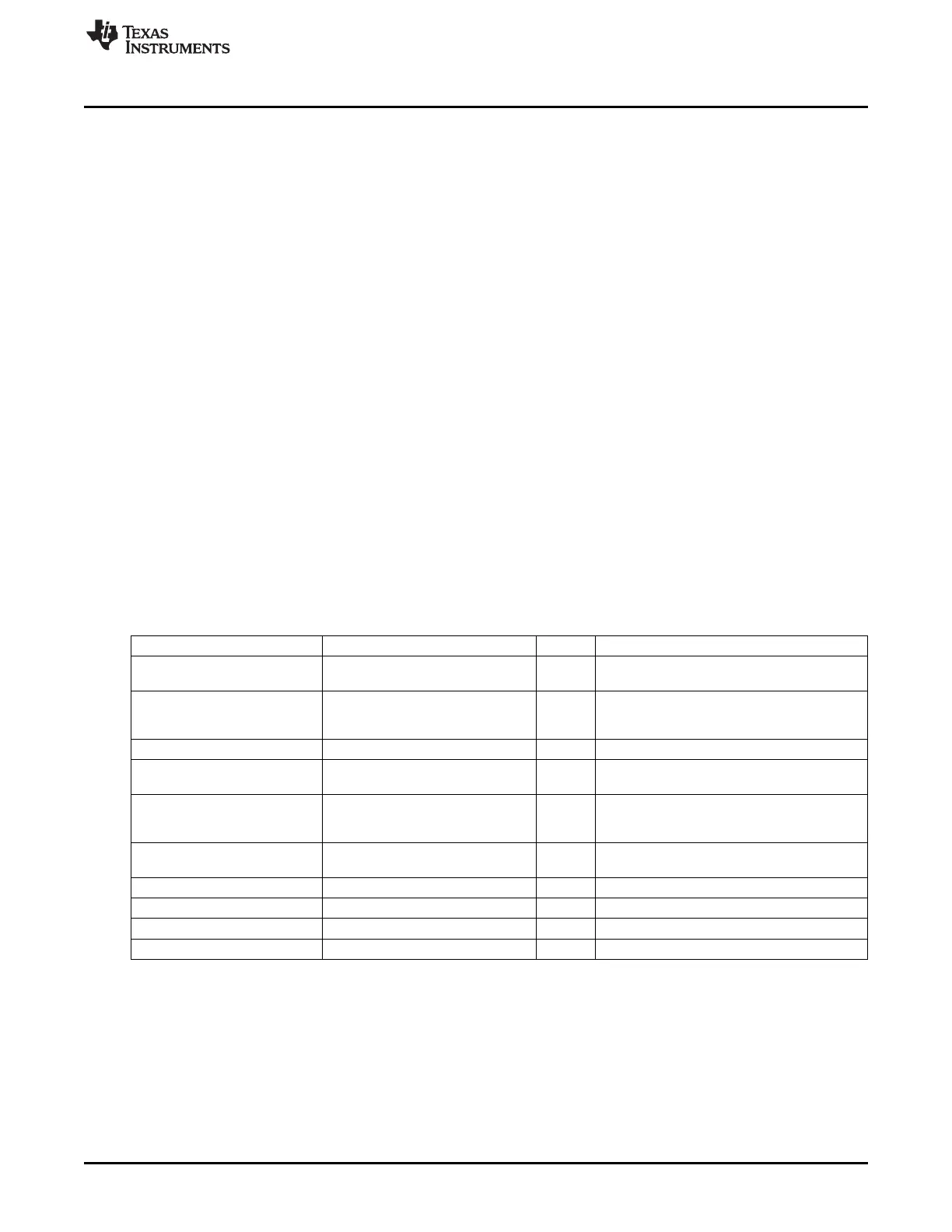

Table 7-23. Write-Posting Mode Configuration

Bit Field Register Value Comments

STARTENGINE GPMC_PREFETCH_CONTROL 0 Write-posting engine can be configured only if

STARTENGINE is cleared to 0.

ENGINECSSELECTOR GPMC_PREFETCH_CONFIG1 0 to 3h Selects the chip-select associated with a

NAND device where the prefetch engine is

active

ACCESSMODE GPMC_PREFETCH_CONFIG1 1 Selects write-posting mode

FIFOTHRESHOLD GPMC_PREFETCH_CONFIG1 Selects the maximum number of bytes read or

written by the host on DMA or interrupt request

TRANSFERCOUNT GPMC_PREFETCH_CONFIG2 Selects the number of bytes to be read or

written by the engine from/to the selected chip-

select

SYNCHROMODE GPMC_PREFETCH_CONFIG1 0 Engine starts the access to chip-select as soon

as STARTENGINE is set.

ENABLEOPTIMIZEDACCESS GPMC_PREFETCH_CONFIG1 0/1 See Section 7.1.3.3.12.4.6

CYCLEOPTIMIZATION GPMC_PREFETCH_CONFIG

ENABLEENGINE GPMC_PREFETCH_CONFIG1 1 Engine enabled

STARTENGINE GPMC_PREFETCH_CONTROL 1 Starts the prefetch engine

331

SPRUH73H–October 2011–Revised April 2013 Memory Subsystem

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...