Multimedia Card Registers

www.ti.com

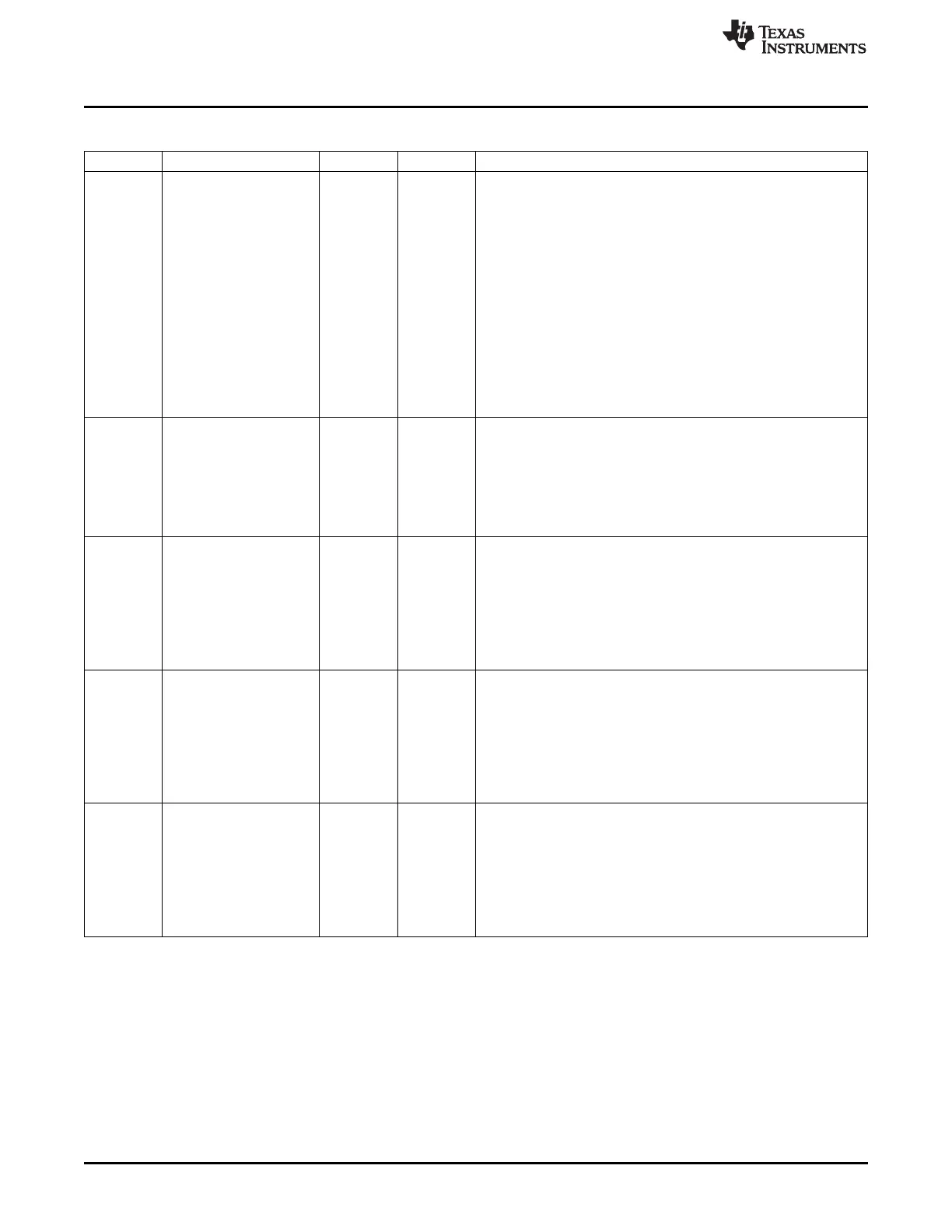

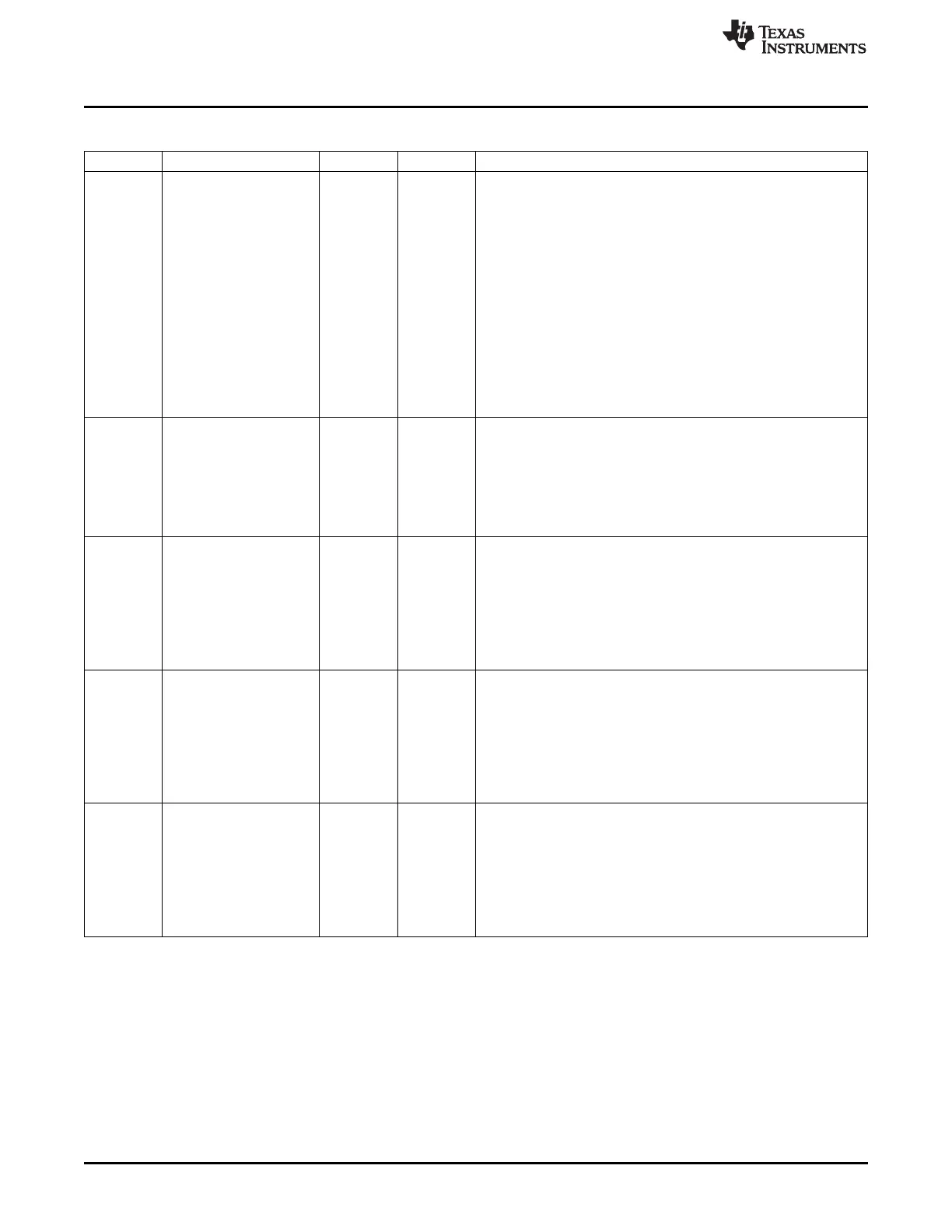

Table 18-38. SD_STAT Register Field Descriptions (continued)

Bit Field Type Reset Description

4 BWR R/W 0h Buffer write ready.

This bit is set automatically during a write operation to the card (see

class

4 - block oriented write command) when the host can write a

complete block as specified by SD_BLK

[10:0] BLEN.

It indicates that the memory card has emptied one block from the

buffer and that the local host is able to write one block of data into

the buffer.

Note: If the DMA transmit mode is enabled, this bit is never set

instead, a DMA transmit request to the main DMA controller of the

system is generated.

0x0(W) = Status bit unchanged

0x0(R) = Not ready to write buffer

0x1(W) = Status is cleared.

0x1(R) = Ready to write buffer

3 DMA R/W 0h DMA Interrupt.

This status is set when an interrupt is required in the ADMA

instruction and after the data transfer completion.

0x0(W) = Status bit unchanged

0x0(R) = DMA Interrupt detected

0x1(W) = Status is cleared.

0x1(R) = No DMA Interrupt

2 BGE R/W 0h Block gap event.

When a stop at block gap is requested (SD_HCTL[16] SBGR bit),

this bit is automatically set when transaction is stopped at the block

gap during a read or write operation.

0x0(W) = Status bit unchanged

0x0(R) = No block gap event

0x1(W) = Status is cleared

0x1(R) = Transaction stopped at block gap

1 TC R/W 0h Transfer completed.

This bit is always set when a read/write transfer is completed or

between two blocks when the transfer is stopped due to a stop at

block gap request (SD_HCTL[16] SBGR bit).

0x0(W) = Status bit unchanged

0x0(R) = No transfer complete

0x1(W) = Status is cleared

0x1(R) = Data transfer complete

0 CC R/W 0h Command complete.

This bit is set when a

1-to-0 transition occurs in the register command inhibit

(SD_PSTATE[0] CMDI bit)

0x0(W) = Status bit unchanged

0x0(R) = No command complete

0x1(W) = Status is cleared

0x1(R) = Command complete

3428

Multimedia Card (MMC) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...