Multimedia Card Registers

www.ti.com

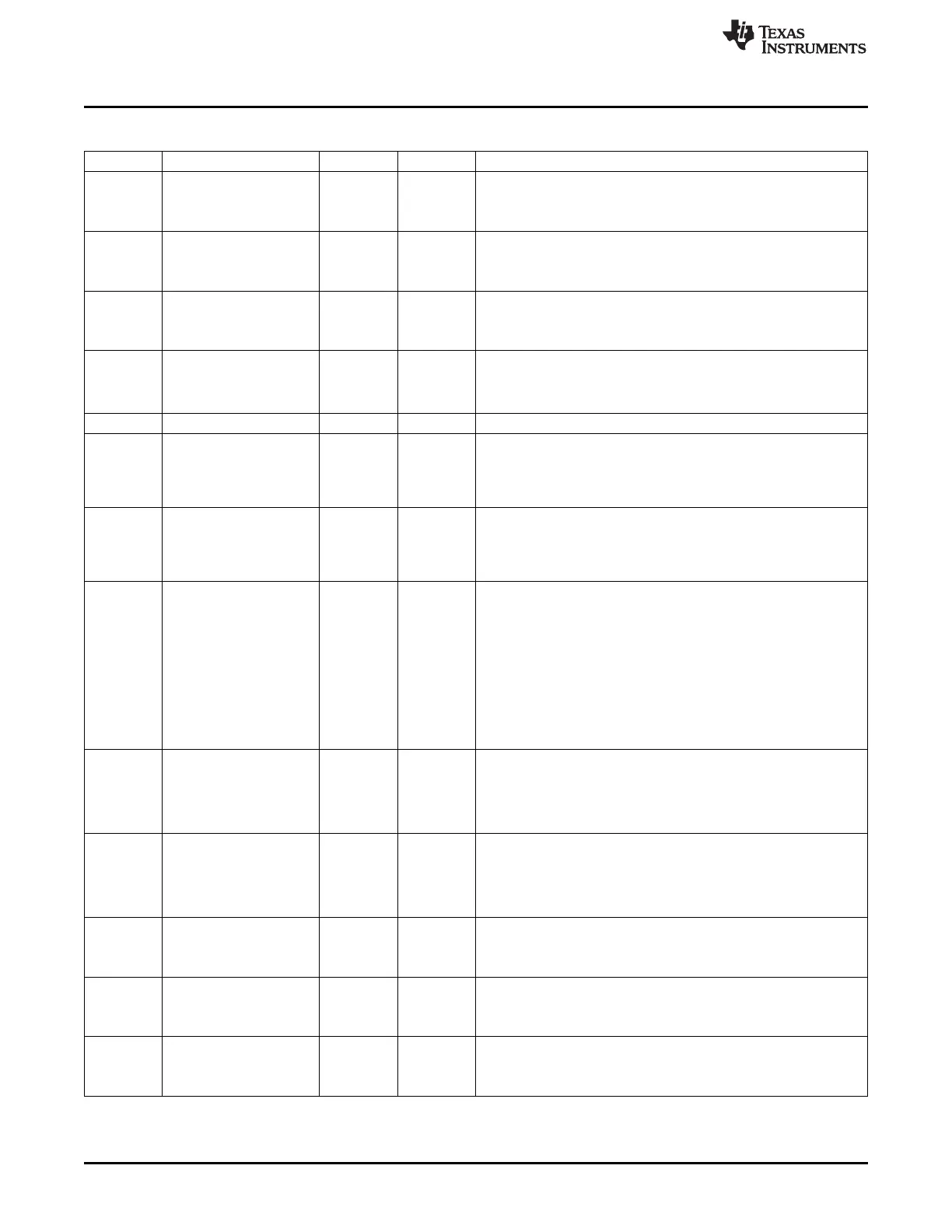

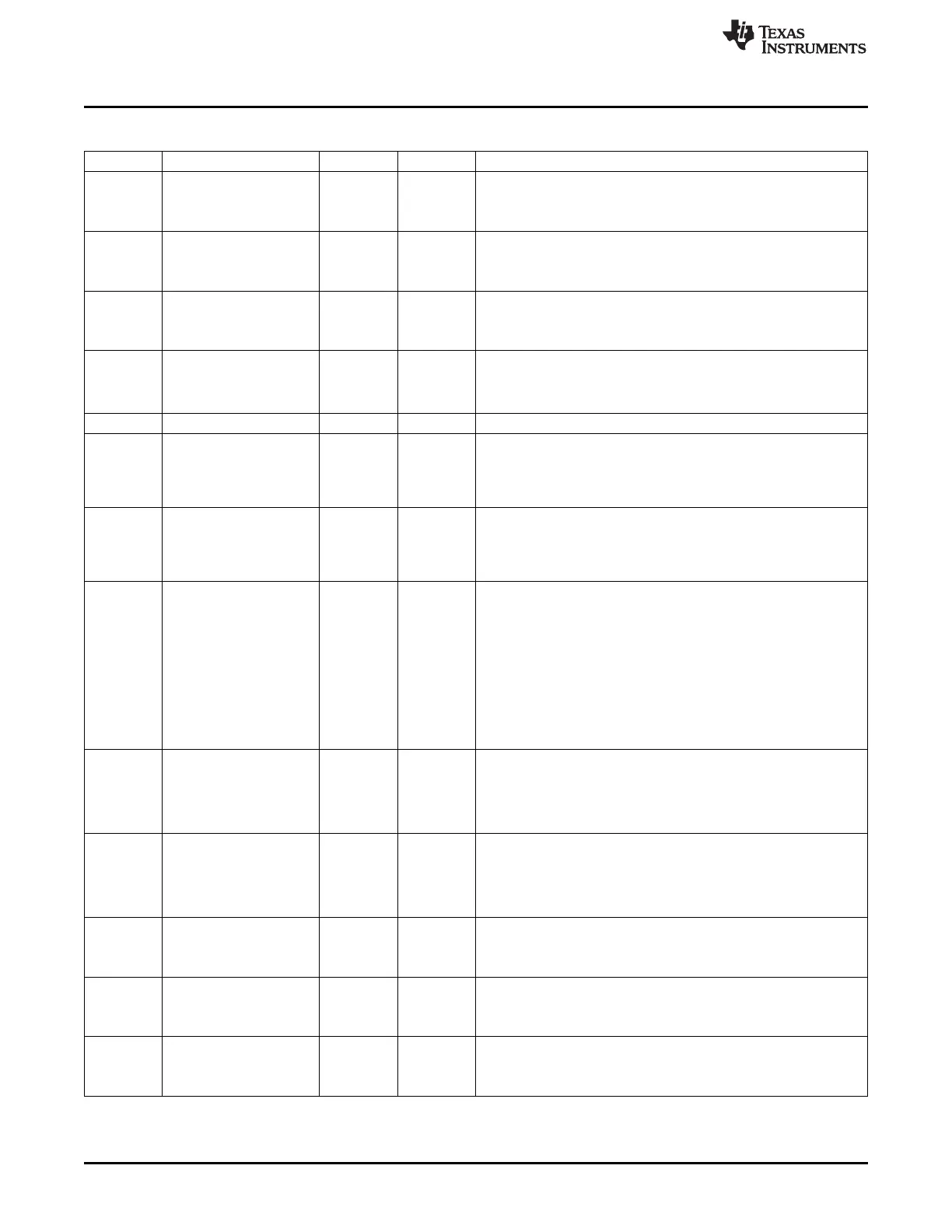

Table 18-39. SD_IE Register Field Descriptions (continued)

Bit Field Type Reset Description

18 CEB_ENABLE R/W 0h

Command end bit error interrupt enable

0x0 = Masked

0x1 = Enabled

17 CCRC_ENABLE R/W 0h

Command CRC error interrupt enable

0x0 = Masked

0x1 = Enabled

16 CTO_ENABLE R/W 0h

Command timeout error interrupt enable

0x0 = Masked

0x1 = Enabled

15 NULL R 0h Fixed to 0.

The host driver shall control error interrupts using the Error Interrupt

Signal Enable register.

Writes to this bit are ignored.

14-11 Reserved R 0h

10 BSR_ENABLE R/W 0h

Boot Status Interrupt Enable A write to this register when

SD_CON[BOOT] is cleared to 0 is ignored.

0x0 = Masked

0x1 = Enabled

9 OBI_ENABLE R/W 0h

Out-of-band interrupt enable A write to this register when

SD_CON[14] OBIE is cleared to 0 is ignored.

0x0 = Masked

0x1 = Enabled

8 CIRQ_ENABLE R/W 0h Card interrupt enable.

A clear of this bit also clears the corresponding status bit.

During

1-bit mode, if the interrupt routine does not remove the source of a

card interrupt in the SDIO card, the status bit is reasserted when this

bit is set to 1.

This bit must be set to 1 when entering in smart idle mode to enable

system to identity wake-up event and to allow controller to clear

internal wake-up source.

0x0 = Masked

0x1 = Enabled

7 CREM_ENABLE R/W 0h Card Removal interrupt Enable This bit must be set to 1 when

entering in smart idle mode to enable system to identity wake-up

event and to allow controller to clear internal wake-up source.

0x0 = Masked

0x1 = Enabled

6 CINS_ENABLE R/W 0h Card Insertion interrupt Enable This bit must be set to 1 when

entering in smart idle mode to enable system to identity wake-up

event and to allow controller to clear internal wake-up source.

0x0 = Masked

0x1 = Enabled

5 BRR_ENABLE R/W 0h

Buffer read ready interrupt enable

0x0 = Masked

0x1 = Enabled

4 BWR_ENABLE R/W 0h

Buffer write ready interrupt enable

0x0 = Masked

0x1 = Enabled

3 DMA_ENABLE R/W 0h

DMA interrupt enable

0x0 = Masked

0x1 = Enable

3430

Multimedia Card (MMC) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...