www.ti.com

DCAN Registers

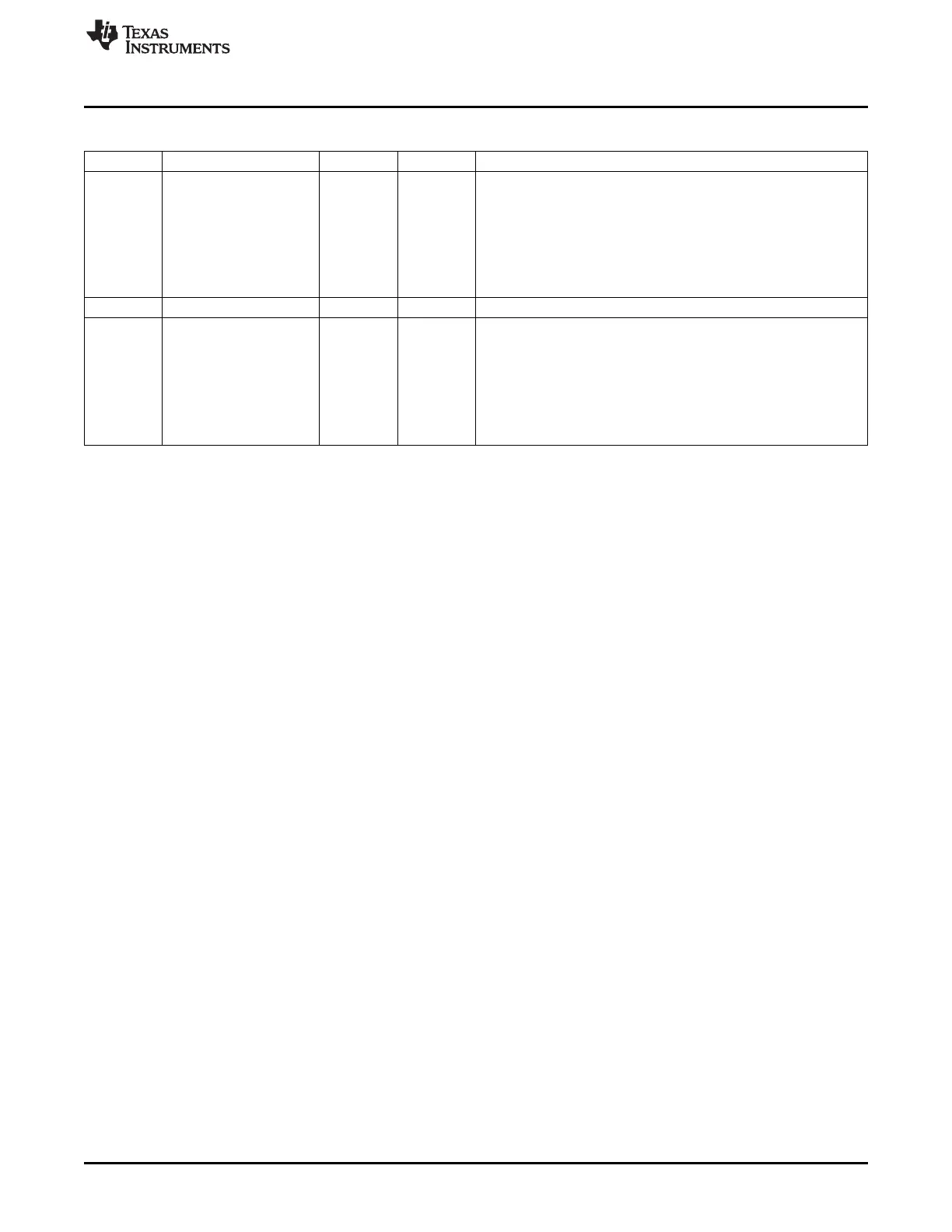

Table 23-46. IF1CMD Register Field Descriptions (continued)

Bit Field Type Reset Description

14 DMAactive R/WP 0h Activation of DMA feature for subsequent internal IF1 update.

Note: Due to the auto reset feature of the DMAactive bit, this bit has

to be set for each subsequent DMA cycle separately.

0x0 = DMA request line is independent of IF1 activities.

0x1 = DMA is requested after completed transfer between IF1

register set and message RAM. The DMA request remains active

until the first read or write to one of the IF1 registers; an exception is

a write to Message Number (Bits [7:0]) when DMAactive is one.

13-8 Reserved R 0h

7-0 Message_Number R/WP 0h

Number of message object in message RAM which is used for data

transfer.

0x00 = Invalid message number.

0x01 = Valid message numbers (value 01 to 80).

0x80 = Valid message number.

0x81 = Invalid message numbers (value 81 to FF).

0xff = Invalid message numbers.

3961

SPRUH73H–October 2011–Revised April 2013 Controller Area Network (CAN)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...