Power, Reset, and Clock Management

www.ti.com

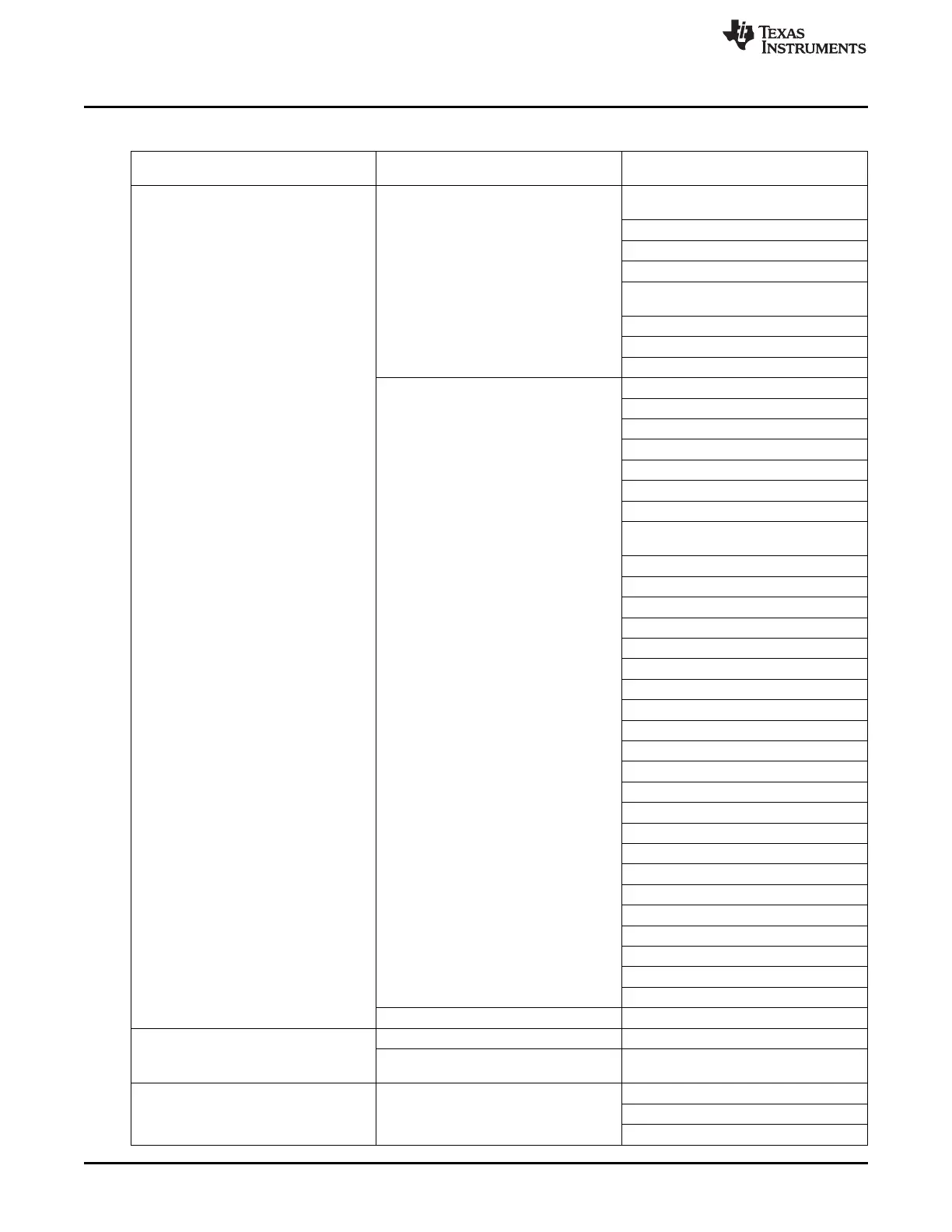

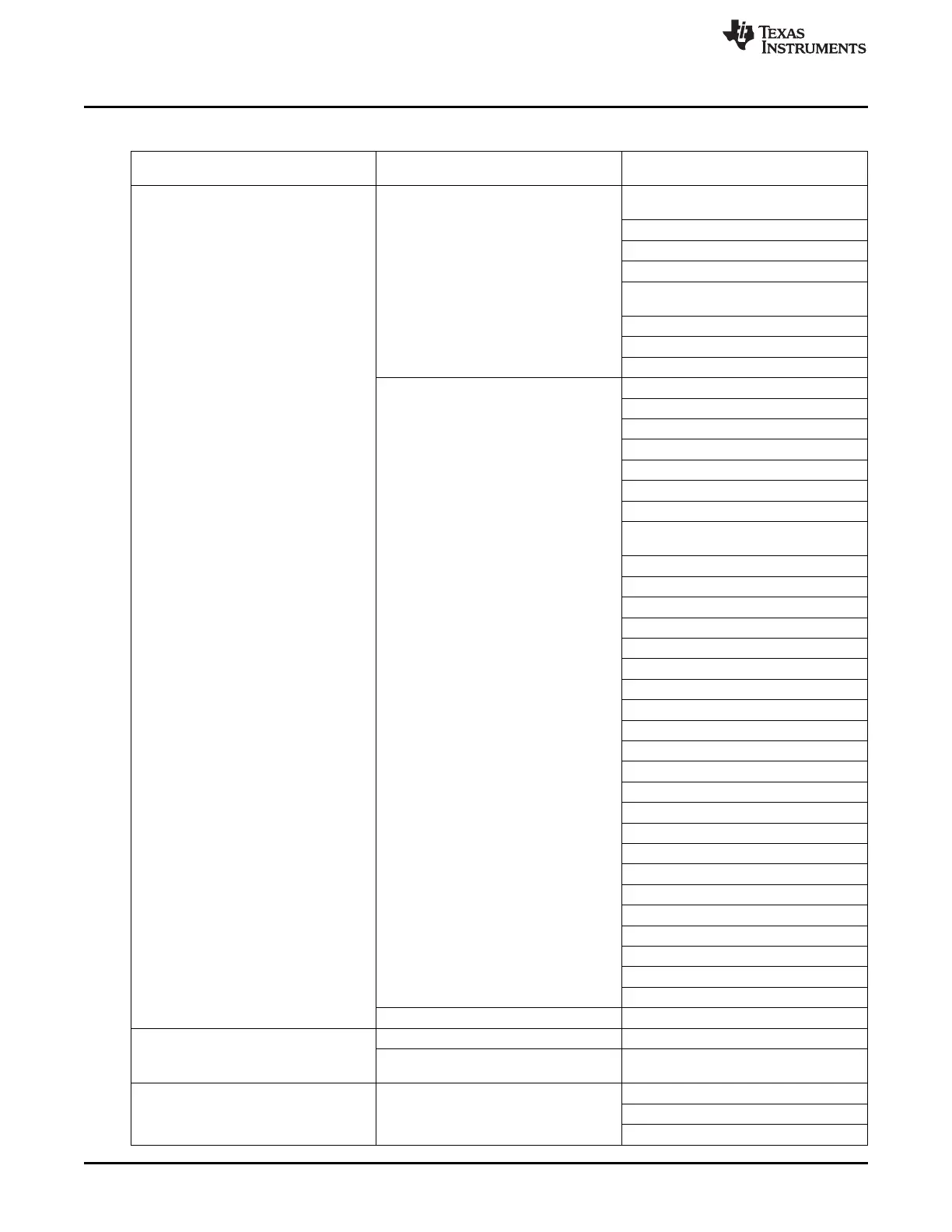

Table 8-28. Power Domain of Various Modules (continued)

Power Supply Power Domain Modules OR Supply Destinations

(sinks)

Toplevel: Pinmux gates/logic, oscillator

wake logic

DDR PHY (DIDs)

WKUP_DFTSS

Debugs

Digital section (VDD) of CORE PLL, PER

PLL, Display PLL and DDR PLL

Emulation sections of MPU

VDD of all IOs including crystal oscillators

RC Oscillator

Infrastructure:

L3

L4_PER, L4_Fast, L4_FW

VDD_CORE EMIF4

EDMA

GPMC

OCMC controller

L3 / L4_PER / L4_Fast / L4_FW

Peripherals

PRU-ICSS

LCD controller

Ethernet Switch

USB Controller

GPMC

MMC0..2

DMTIMER2..7

PD_PER Uart1..5

SPI0, 1

I2C1, 2

DCAN0, 1

McASP0, 1

ePWM0..2

eCAP0..2

eQeP0,1

GPIO1..3

ELM

Mailbox0, Spinlock

OCP_WP

Others:

USB2PHYCORE (VDD/digital section)

USB2PHYCM (VDD/digital section)

PD_GFX SGX530

PD_MPU CPU, L1, L2 of MPU

VDD_MPU Interrupt controller of MPU Subsystem

PD_WKUP

Digital Portion (VDD) of MPU PLL

1. RTC

VDD_RTC PD_RTC VDD for 32 768 Hz Crystal Osc

VDD for IO for the alarm pin

546

Power, Reset, and Clock Management (PRCM) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...