Power, Reset, and Clock Management

www.ti.com

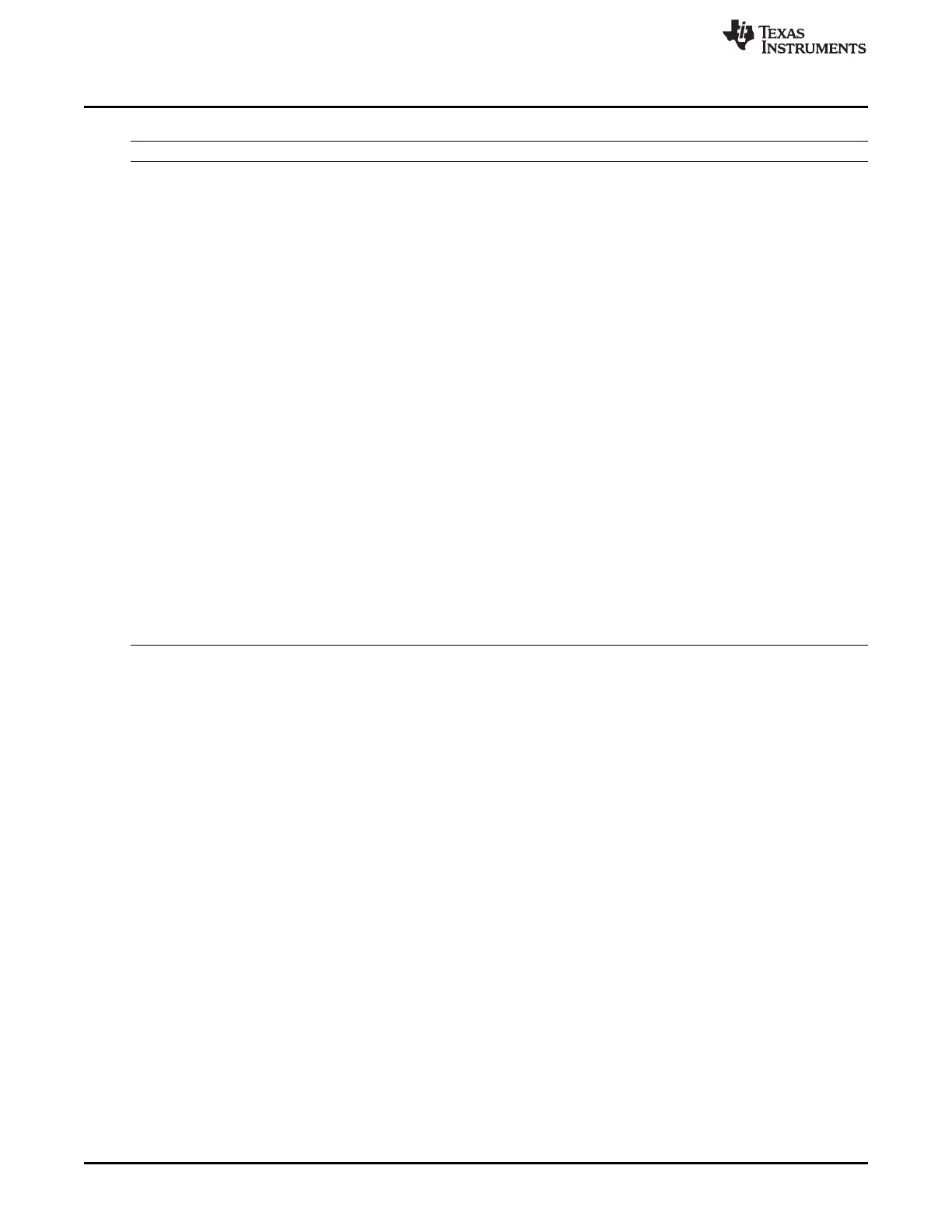

Table 8-146. CM_DPLL REGISTERS

Offset Acronym Register Name Section

4h CLKSEL_TIMER7_CLK Selects the Mux select line for TIMER7 clock [warm Section 8.1.12.3.1

reset insensitive]

8h CLKSEL_TIMER2_CLK Selects the Mux select line for TIMER2 clock [warm Section 8.1.12.3.2

reset insensitive]

Ch CLKSEL_TIMER3_CLK Selects the Mux select line for TIMER3 clock [warm Section 8.1.12.3.3

reset insensitive]

10h CLKSEL_TIMER4_CLK Selects the Mux select line for TIMER4 clock [warm Section 8.1.12.3.4

reset insensitive]

14h CM_MAC_CLKSEL Selects the clock divide ration for MII clock [warm reset Section 8.1.12.3.5

insensitive]

18h CLKSEL_TIMER5_CLK Selects the Mux select line for TIMER5 clock [warm Section 8.1.12.3.6

reset insensitive]

1Ch CLKSEL_TIMER6_CLK Selects the Mux select line for TIMER6 clock [warm Section 8.1.12.3.7

reset insensitive]

20h CM_CPTS_RFT_CLKSEL Selects the Mux select line for CPTS RFT clock [warm Section 8.1.12.3.8

reset insensitive]

28h CLKSEL_TIMER1MS_CLK Selects the Mux select line for TIMER1 clock [warm Section 8.1.12.3.9

reset insensitive]

2Ch CLKSEL_GFX_FCLK Selects the divider value for GFX clock [warm reset Section 8.1.12.3.10

insensitive]

30h CLKSEL_PRU_ICSS_OCP_CLK Controls the Mux select line for PRU-ICSS OCP clock Section 8.1.12.3.11

[warm reset insensitive]

34h CLKSEL_LCDC_PIXEL_CLK Controls the Mux select line for LCDC PIXEL clock Section 8.1.12.3.12

[warm reset insensitive]

38h CLKSEL_WDT1_CLK Selects the Mux select line for Watchdog1 clock [warm Section 8.1.12.3.13

reset insensitive]

3Ch CLKSEL_GPIO0_DBCLK Selects the Mux select line for GPIO0 debounce clock Section 8.1.12.3.14

[warm reset insensitive]

674

Power, Reset, and Clock Management (PRCM) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...