CONTROL_MODULE Registers

www.ti.com

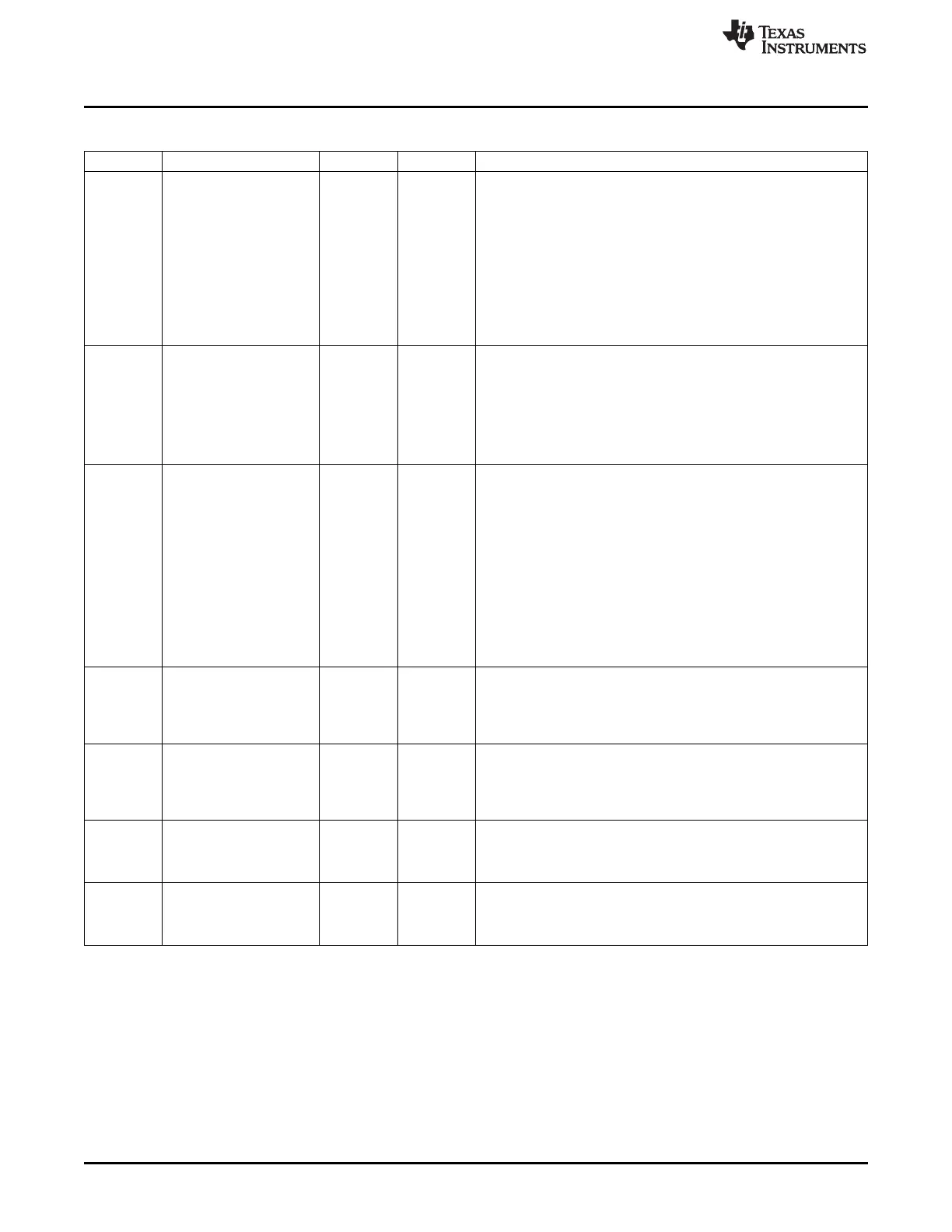

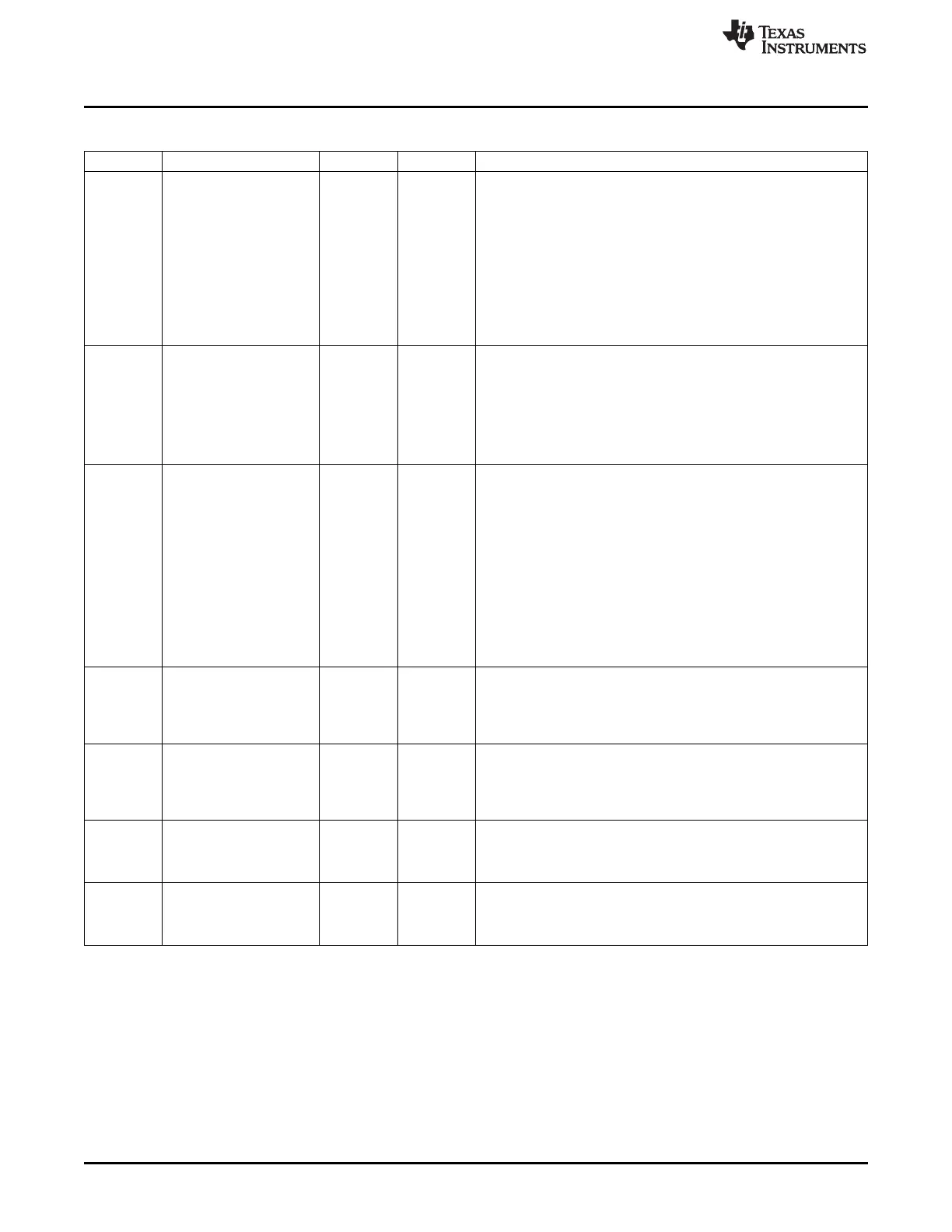

Table 9-101. ddr_data0_ioctrl Register Field Descriptions (continued)

Bit Field Type Reset Description

19 io_config_wd0_dqs R/W 0h Input that selects pullup or pulldown for DDR_DQS0 and

DDR_DQSn0.

Used with io_config_wd1_dqs to define pullup/pulldown according to

the following:

WD1:WD0

00b: Pullup/Pulldown disabled for both DDR_DQS0 and

DDR_DQSn0

01b: Enable weak pullup for DDR_DQS0 and weak pulldown for

DDR_DQSn0

10b: Enable weak pulldown for DDR_DQS0 and weak pullup for

DDR_DQSn0

11b: Weak keeper enabled for both DDR_DQS0 and DDR_DQSn0

18 io_config_wd0_dm R/W 0h Input that selects pullup or pulldown for DM.

Used with io_config_wd1_dm to define pullup/pulldown according to

the following:

WD1:WD0

00: Pullup/Pulldown disabled

01: Weak pullup enabled

10: Weak pulldown enabled

11: Weak keeper enabled

17-10 io_config_wd0_dq R/W 0h Input that selects pullup or pulldown for DQ.

There are 2 bits per IO: io_config_wd1_dq and io_config_wd0_dq.

For example:

macro pin 0: WD1 is bit 20, WD0 is bit 10

macro pin 1: WD1 is bit 21, WD0 is bit 11

...

macro pin 7: WD1 is bit 27, WD0 is bit 17

See the DDR PHY to IO Pin Mapping table in the Control Module

Functional Description section for a mapping of macro bits to I/Os.

WD1:WD0

00: Pullup/Pulldown disabled

01: Weak pullup enabled

10: Weak pulldown enabled

11: Weak keeper enabled

9-8 io_config_sr_clk R/W 0h 2 bit to program clock IO Pads (DDR_DQS/DDR_DQSn) output slew

rate.

These connect as SR1, SR0 of the corresponding IO buffer.

See the DDR Slew Rate Control Settings table in the Control Module

Functional Description section for a definition of these bits.

7-5 io_config_i_clk R/W 0h 3-bit configuration input to program clock IO pads

(DDR_DQS/DDR_DQSn) output impedance.

These connect as I2, I1, I0 of the corresponding buffer.

See the DDR Impedance Control Settings table in the Control

Module Functional Description section for a definition of these bits.

4-3 io_config_sr R/W 0h 2 bit to program data IO Pads output slew rate.

These connect as SR1, SR0 of the corresponding IO buffer.

See the DDR Slew Rate Control Settings table in the Control Module

Functional Description section for a definition of these bits.

2-0 io_config_i R/W 0h 3-bit configuration input to program data IO output impedance.

These connect as I2, I1, I0 of the corresponding IO buffer.

See the DDR Impedance Control Settings table in the Control

Module Functional Description section for a definition of these bits.

860

Control Module SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...