Event

register

(ER/ERH)

Event

enable

register

(EER/EERH)

Event

set

register

(ESR/ESRH)

Chained

event

register

(CER/CERH)

QDMA

event

register

(QER)

64

64

64

64:1 priority encoder

8:1 priority encoder

8

Event queues

Channel mapping

Queue bypass

Parameter

set 0

Parameter

set 1

set 255

Parameter

Parameter

set 254

Transfer request process submit

PaRAM

E63 E0E1

To

TC(S)

From

EDMA3TC0

From

EDMA3TC3

Completion

interface

Completion

detection

Event

trigger

Manual

trigger

Chain

trigger

Completion

interruptdetection

Error

EDMA3CC_INT[7:0]

From peripherals/external events

EDMA3CC_ERRINT

QDMA trigger

Memory

protection

Read/

write to/

from CPU

EDMA3CC_

MPINT

To chained event register (CER/CERH)

0

15

EDMA3

channel

controller

Early completion

Queue 0

0

15

Queue 1

015

Queue 2

015

Queue 3

www.ti.com

Functional Description

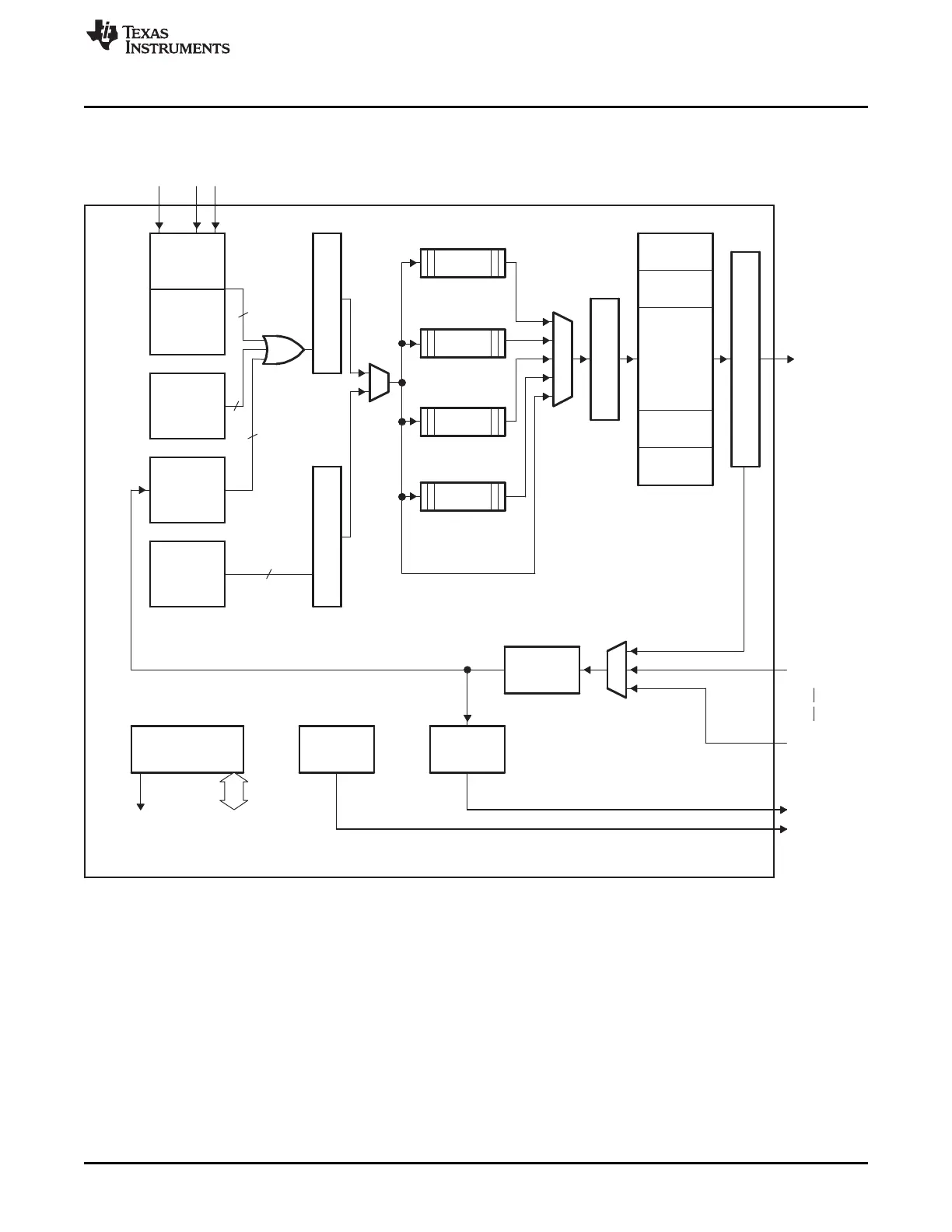

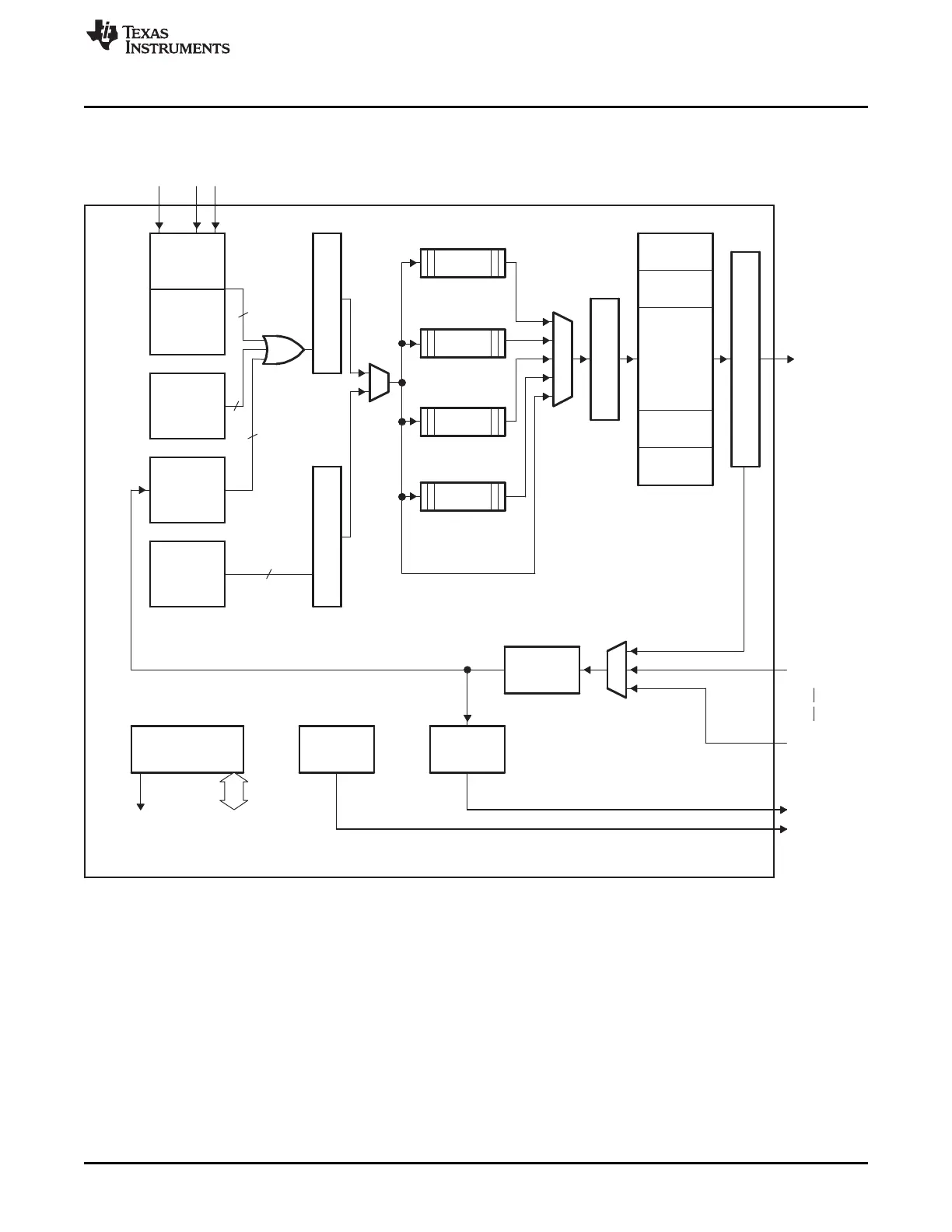

Figure 11-4. EDMA3 Channel Controller (EDMA3CC) Block Diagram

A trigger event is needed to initiate a transfer. A trigger event may be due to an external event, manual

write to the event set register, or chained event for DMA channels. QDMA channels auto-trigger when a

write to the trigger word that you program occurs on the associated PaRAM set. All such trigger events

are logged into appropriate registers upon recognition.

Once a trigger event is recognized, the appropriate event gets queued in the EDMA3CC event queue. The

assignment of each DMA/QDMA channel to an event queue is programmable. Each queue is 16 events

deep; therefore, you can queue up to 16 events (on a single queue) in the EDMA3CC at a time. Additional

pending events that are mapped to a full queue are queued when the event queue space becomes

available. See Section 11.3.11.

If events on different channels are detected simultaneously, the events are queued based on a fixed

priority arbitration scheme with the DMA channels being higher priority events than the QDMA channels.

Among the two groups of channels, the lowest-numbered channel is the highest priority.

877

SPRUH73H–October 2011–Revised April 2013 Enhanced Direct Memory Access (EDMA)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...