ARM Cortex-A8 Memory Map

www.ti.com

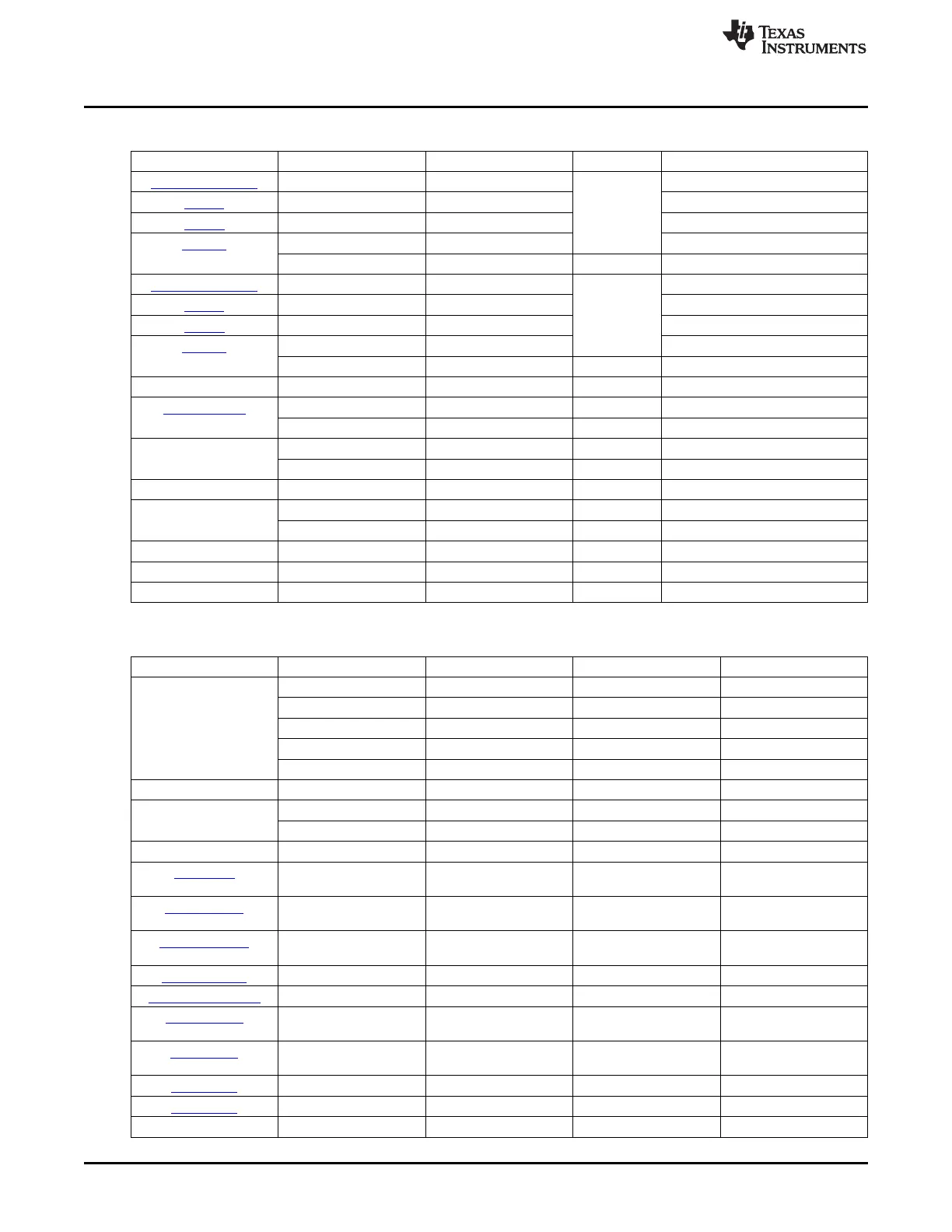

Table 2-3. L4_PER Peripheral Memory Map (continued)

Device Name Start_address (hex) End_address (hex) Size Description

PWM Subsystem 1 0x4830_2000 0x4830_20FF PWMSS1 Configuration Registers

eCAP1 0x4830_2100 0x4830_217F PWMSS eCAP1 Registers

4KB

eQEP1 0x4830_2180 0x4830_21FF PWMSS eQEP1 Registers

ePWM1 0x4830_2200 0x4830_225F PWMSS ePWM1 Registers

0x4830_2260 0x4830_3FFF 4KB Reserved

PWM Subsystem 2 0x4830_4000 0x4830_40FF PWMSS2 Configuration Registers

eCAP2 0x4830_4100 0x4830_417F PWMSS eCAP2 Registers

4KB

eQEP2 0x4830_4180 0x4830_41FF PWMSS eQEP2 Registers

ePWM2 0x4830_4200 0x4830_425F PWMSS ePWM2 Registers

0x4830_4260 0x4830_5FFF 4KB Reserved

Reserved 0x4830_6000 0x4830_DFFF 32KB Reserved

LCD Controller 0x4830_E000 0x4830_EFFF 4KB LCD Registers

0x4830_F000 0x4830_FFFF 4KB Reserved

Reserved 0x4831_0000 0x4831_1FFF 8KB Reserved

0x4831_2000 0x4831_2FFF 4KB Reserved

Reserved 0x4831_3000 0x4831_7FFF 20KB Reserved

Reserved 0x4831_8000 0x4831_BFFF 16KB Reserved

0x4831_C000 0x4831_CFFF 4KB Reserved

Reserved 0x4831_D000 0x4831_FFFF 12KB Reserved

Reserved 0x4832_0000 0x4832_5FFF 16KB Reserved

Reserved 0x4832_6000 0x48FF_FFFF 13MB-152KB Reserved

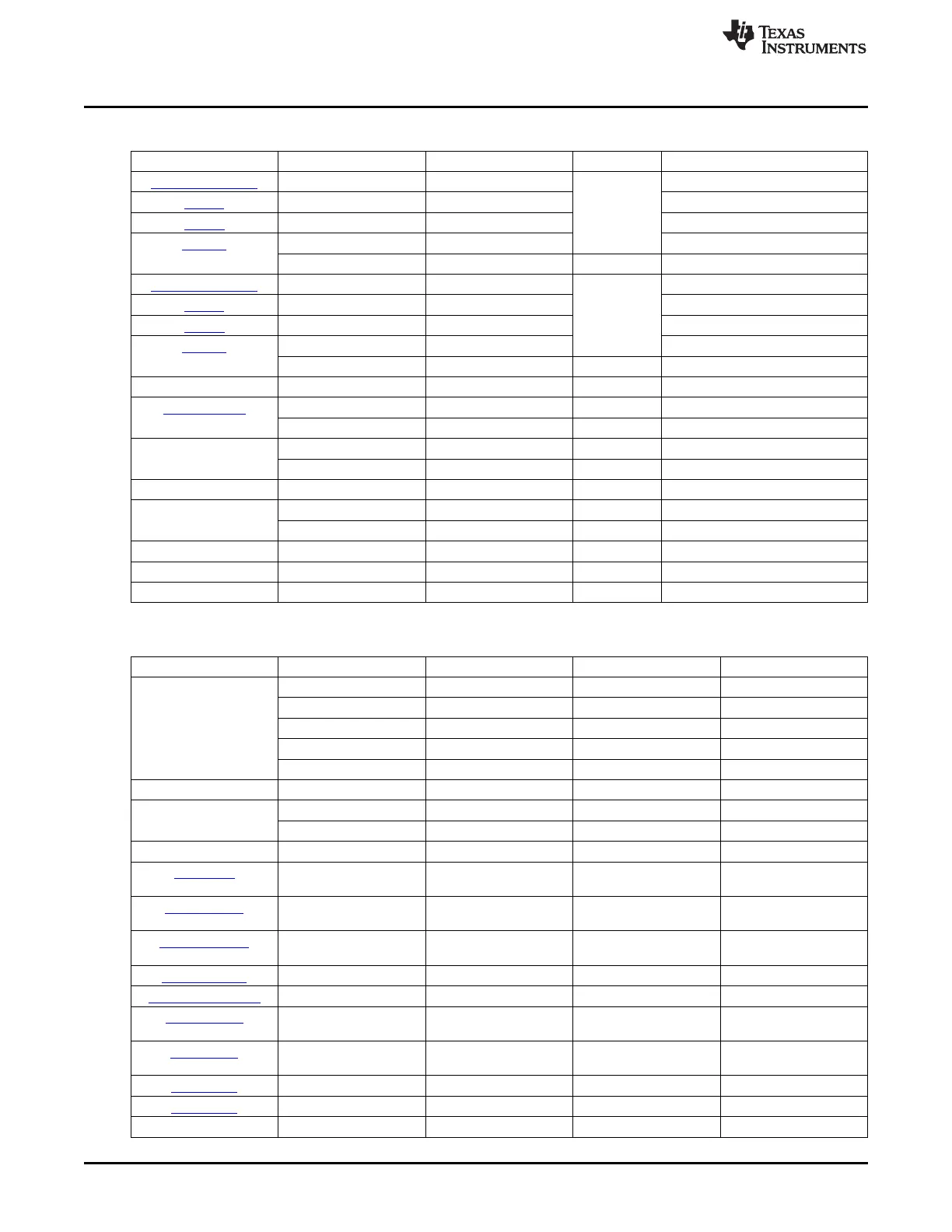

Table 2-4. L4 Fast Peripheral Memory Map

Device Name Start_address (hex) End_address (hex) Size Description

L4_Fast configuration 0x4A00_0000 0x4A00_07FF 2KB Address/Protection (AP)

0x4A00_0800 0x4A00_0FFF 2KB Link Agent (LA)

0x4A00_1000 0x4A00_13FF 1KB Initiator Port (IP0)

0x4A00_1400 0x4A00_17FF 1KB Reserved

0x4A00_1800 0x4A00_1FFF 2KB Reserved (IP2 – IP3)

Reserved 0x4A00_2000 0x4A07_FFFF 504KB Reserved

Reserved 0x4A08_0000 0x4A09_FFFF 128KB Reserved

0x4A0A_0000 0x4A0A_0FFF 4KB Reserved

Reserved 0x4A0A_1000 0x4A0F_FFFF 380KB Reserved

CPSW_SS 0x4A10_0000 0x4A10_7FFF 32KB Ethernet Switch

Subsystem

CPSW_PORT 0x4A10_0100 0x4A10_07FF Ethernet Switch Port

Control

CPSW_CPDMA 0x4A10_0800 0x4A10_08FF CPPI DMA Controller

Module

CPSW_STATS 0x4A10_0900 0x4A10_09FF Ethernet Statistics

CPSW_STATERAM 0x4A10_0A00 0x4A10_0BFF CPPI DMA State RAM

CPSW_CPTS 0x4A10_0C00 0x4A10_0CFF Ethernet Time Sync

Module

CPSW_ALE 0x4A10_0D00 0x4A10_0D7F Ethernet Address

Lookup Engine

CPSW_SL1 0x4A10_0D80 0x4A10_0DBF Ethernet Sliver for Port 1

CPSW_SL2 0x4A10_0DC0 0x4A10_0DFF Ethernet Sliver for Port 2

Reserved 0x4A10_0E00 0x4A10_0FFF Reserved

162

Memory Map SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...