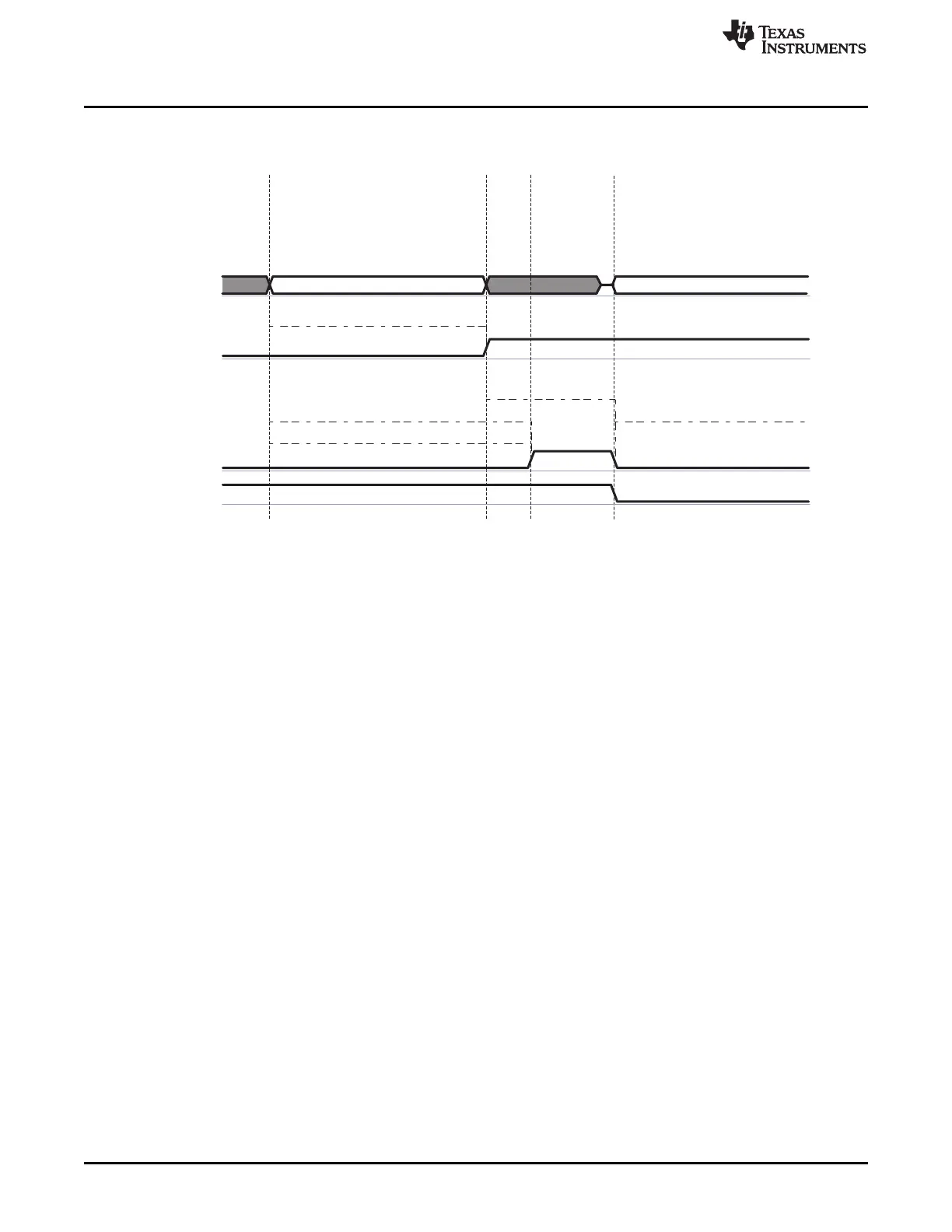

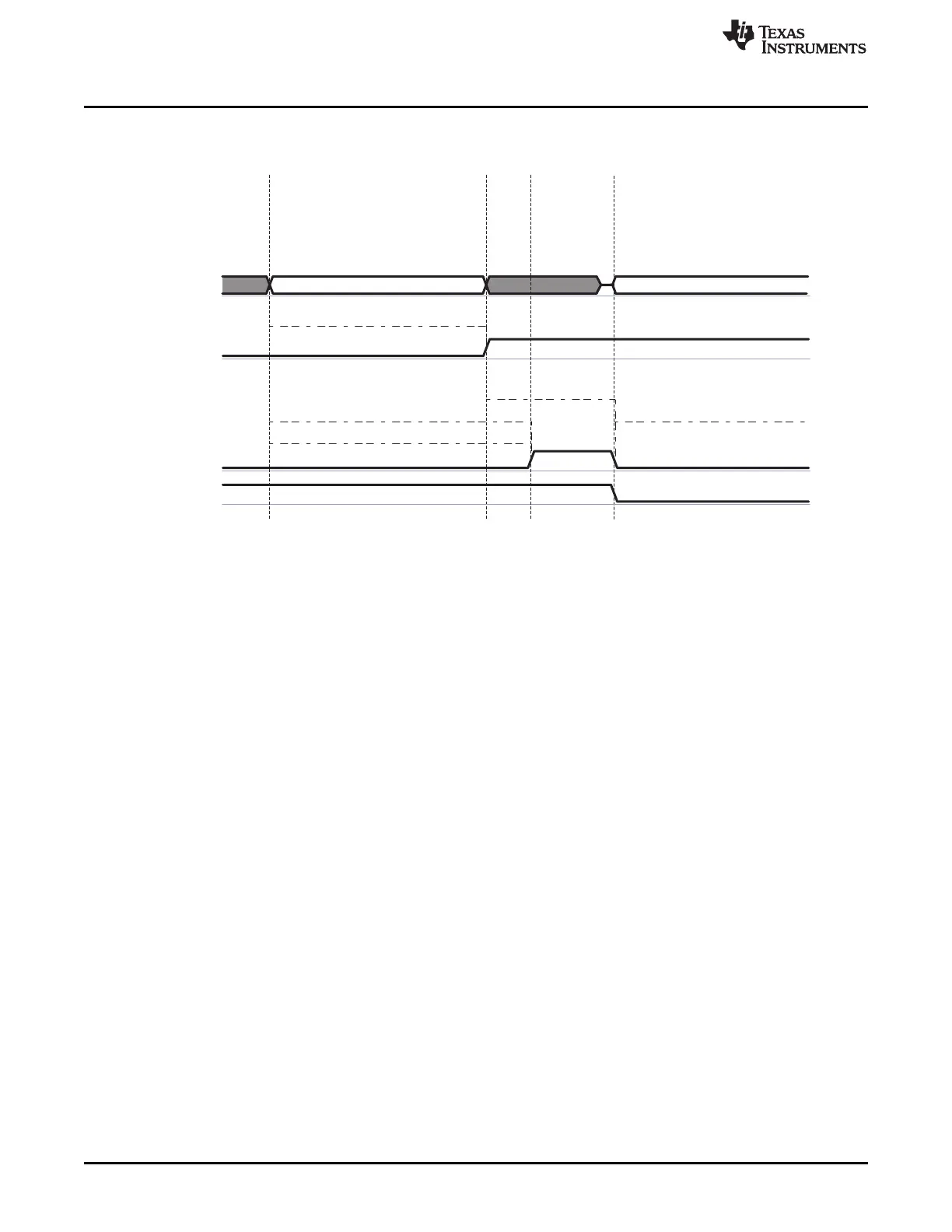

DATA 0 ADD 1

nOE

nCS0

DIR IN OUT

A[16:1]/D[15:0]

OEOFFTIME

BUSTURNAROUND

CSOFFTIME

RDCYCLETIME

RD/WRCYCLETIME

New read/write

access

GPMC

www.ti.com

Figure 7-11. Read to Read / Write for a Address-Data or AAD-Multiplexed Device, On Same CS,

With Bus Turnaround

7.1.3.3.8.3.7.2 Idle Cycles Between Accesses to Same Chip-Select (CYCLE2CYCLESAMECSEN,

CYCLE2CYCLEDELAY)

Some devices require a minimum chip-select signal inactive time between accesses. The

GPMC_CONFIG6_i[7] CYCLE2CYCLESAMECSEN bit enables insertion of a minimum number of

GPMC_FCLK cycles, defined by the GPMC_CONFIG6_i[11-8] CYCLE2CYCLEDELAY field, between

successive accesses of any type (read or write) to the same chip-select.

If CYCLE2CYCLESAMECSEN is enabled, any subsequent access to the same chip-select is delayed until

its CYCLE2CYCLEDELAY completes. The CYCLE2CYCLEDELAY counter starts when

CSRDOFFTIME/CSWROFFTIME completes.

The same applies to successive accesses occurring during 32-bit word or burst accesses split into

successive single accesses when the single-access mode is used (GPMC_CONFIG1_i[30]

READMULTIPLE = 0 or GPMC_CONFIG1_i[28] WRITEMULTIPLE = 0).

All control signals are kept in their default states during these idle GPMC_FCLK cycles. This prevents

back-to-back accesses to the same chip-select without idle cycles between accesses.

7.1.3.3.8.3.7.3 Idle Cycles Between Accesses to Different Chip-Select (CYCLE2CYCLEDIFFCSEN,

CYCLE2CYCLEDELAY)

Because of the pipelined behavior of the system, successive accesses to different chip-selects can occur

back-to-back with no idle cycles between accesses. Depending on the control signals (CSn, ADV_ALEn,

BE0_CLEn, OE_REn, WEn) assertion and de-assertion timing parameters and on the IC timing

parameters, some control signals assertion times may overlap between the successive accesses to

different CS. Similarly, some control signals (WEn, OE_REn) may not respect required transition times.

To work around the overlapping and to observe the required control-signal transitions, a minimum of

CYCLE2CYCLEDELAY inactive cycles is inserted between the access being initiated to this chip-select

and the previous access ending for a different chip-select. This applies to any type of access (read or

write).

272

Memory Subsystem SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...