www.ti.com

GPMC

If GPMC_CONFIG6_i[6] CYCLE2CYCLEDIFFCSEN is enabled, the chip-select access is delayed until

CYCLE2CYCLEDELAY cycles have expired since the end of a previous access to a different chip-select.

CYCLE2CYCLEDELAY count starts at CSRDOFFTIME/CSWROFFTIME completion. All control signals

are kept inactive during the idle GPMC_FCLK cycles.

CYCLE2CYCLESAMECSEN and CYCLE2CYCLEDIFFCSEN should be set in registers to respectively get

idle cycles inserted between accesses on this chip-select and after accesses to a different chip-select.

The CYCLE2CYCLEDELAY delay runs in parallel with the BUSTURNAROUND delay. It should be noted

that BUSTURNAROUND is a timing parameter defined for the ending chip-select access, whereas

CYCLE2CYCLEDELAY is a timing parameter defined for the starting chip-select access. The effective

minimum delay between successive accesses is based on the larger delay timing parameter and on

access type combination, since bus turnaround does not apply to all access types. See

Section 7.1.3.3.8.3.7.1 for more details on bus turnaround.

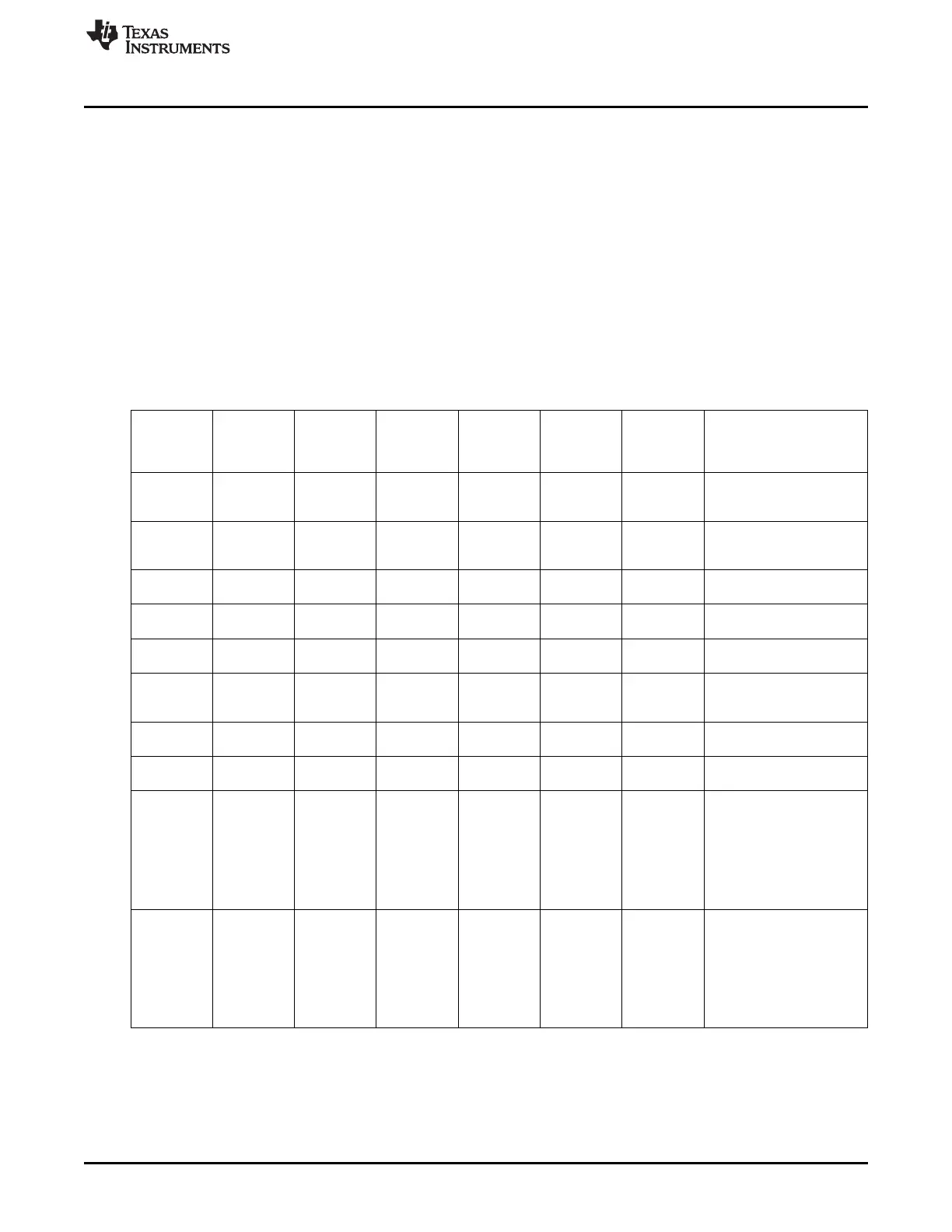

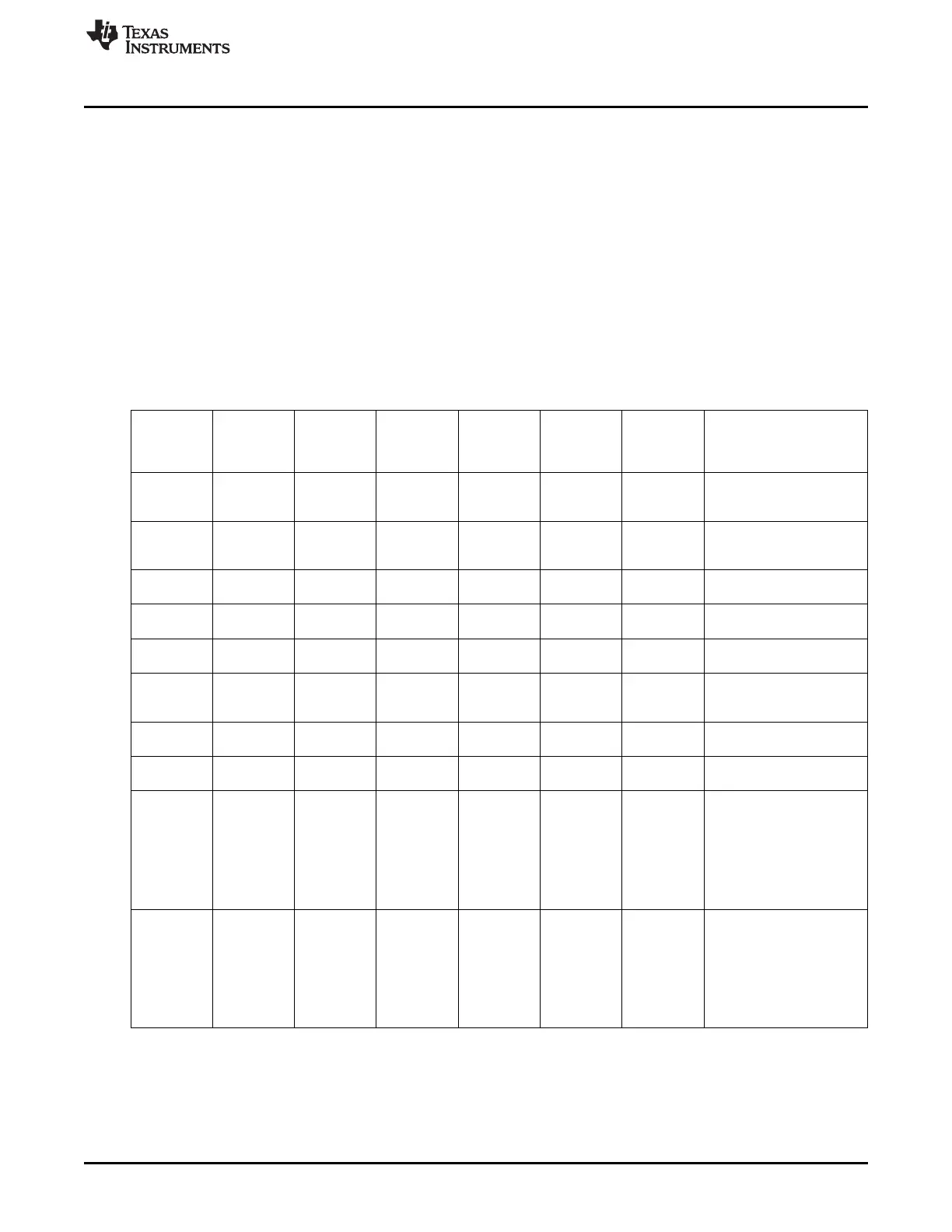

Table 7-10 describes the configuration required for idle cycle insertion.

Table 7-10. Idle Cycle Insertion Configuration

BUSTURN CYCLE2 CYCLE2

First Second Idle Cycle Insertion

AROUND Addr/Data CYCLE CYCLE

Access Access Chip-Select Between the Two

Timing Multiplexed SAMECSEN DIFFCSEN

Type Type Accesses

Parameter Parameter Parameter

No idle cycles are inserted

R/W 0 R/W Any Any 0 x if the two accesses are well

pipelined.

No idle cycles are inserted

R >0 R Same Nonmuxed x 0 if the two accesses are well

pipelined.

BUSTURNAROUND cycles

R >0 R Different Nonmuxed 0 0

are inserted.

BUSTURNAROUND cycles

R >0 R/W Any Muxed 0 0

are inserted.

BUSTURNAROUND cycles

R >0 W Any Any 0 0

are inserted.

No idle cycles are inserted

W >0 R/W Any Any 0 0 if the two accesses are well

pipelined.

CYCLE2CYCLEDELAY

R/W 0 R/W Same Any 1 x

cycles are inserted.

CYCLE2CYCLEDELAY

R/W 0 R/W Different Any x 1

cycles are inserted.

CYCLE2CYCLEDELAY

cycles are inserted. If BTA

idle cycles already apply on

these two back-to-back

R/W >0 R/W Same Any 1 x

accesses, the effective

delay is max

(BUSTURNAROUND,

CYCLE2CYCLEDELAY).

CYCLE2CYCLEDELAY

cycles are inserted. If BTA

idle cycles already apply on

these two back-to-back

R/W >0 R/W Different Any x 1

accesses, the effective

delay is maximum

(BUSTURNAROUND,

CYCLE2CYCLEDELAY).

273

SPRUH73H–October 2011–Revised April 2013 Memory Subsystem

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...