www.ti.com

Multimedia Card Registers

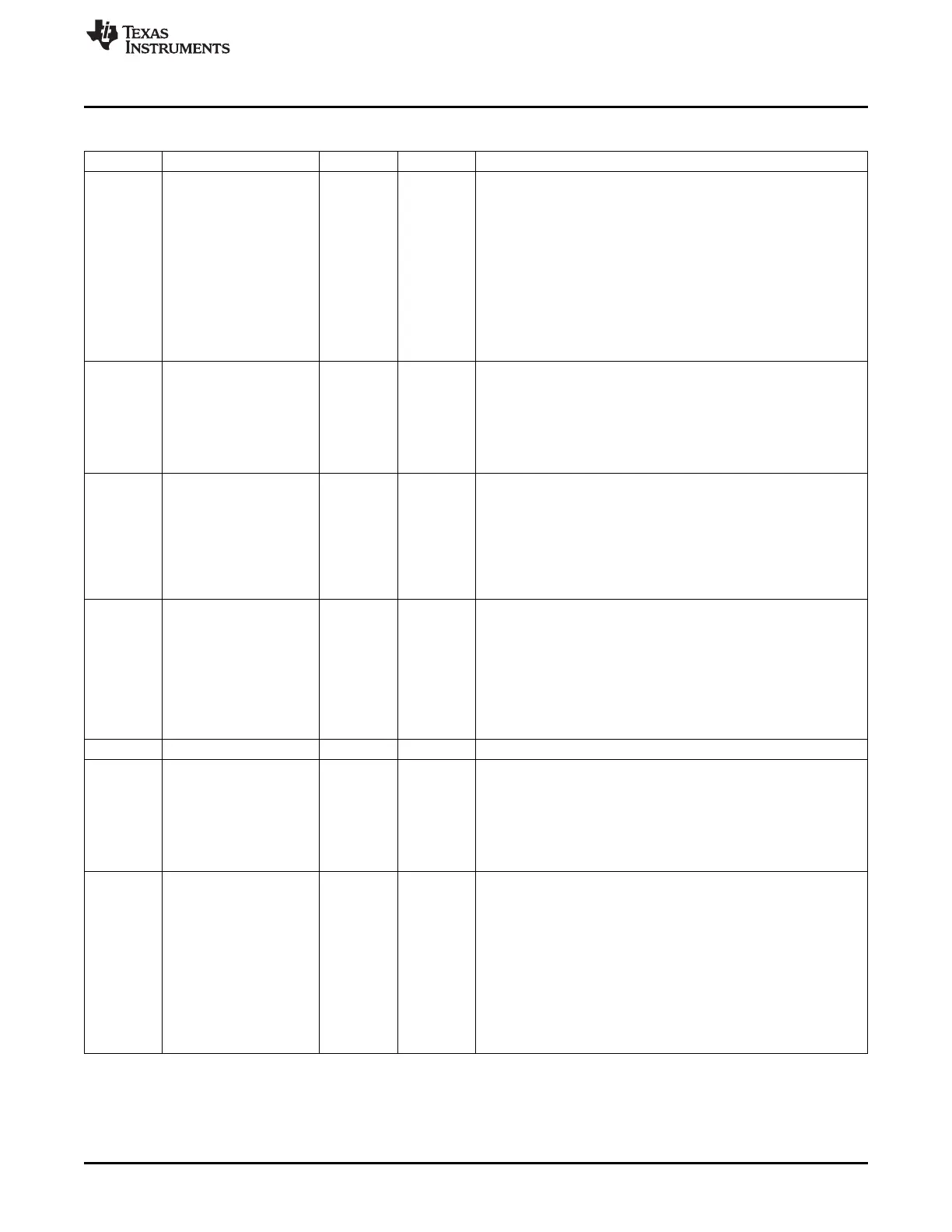

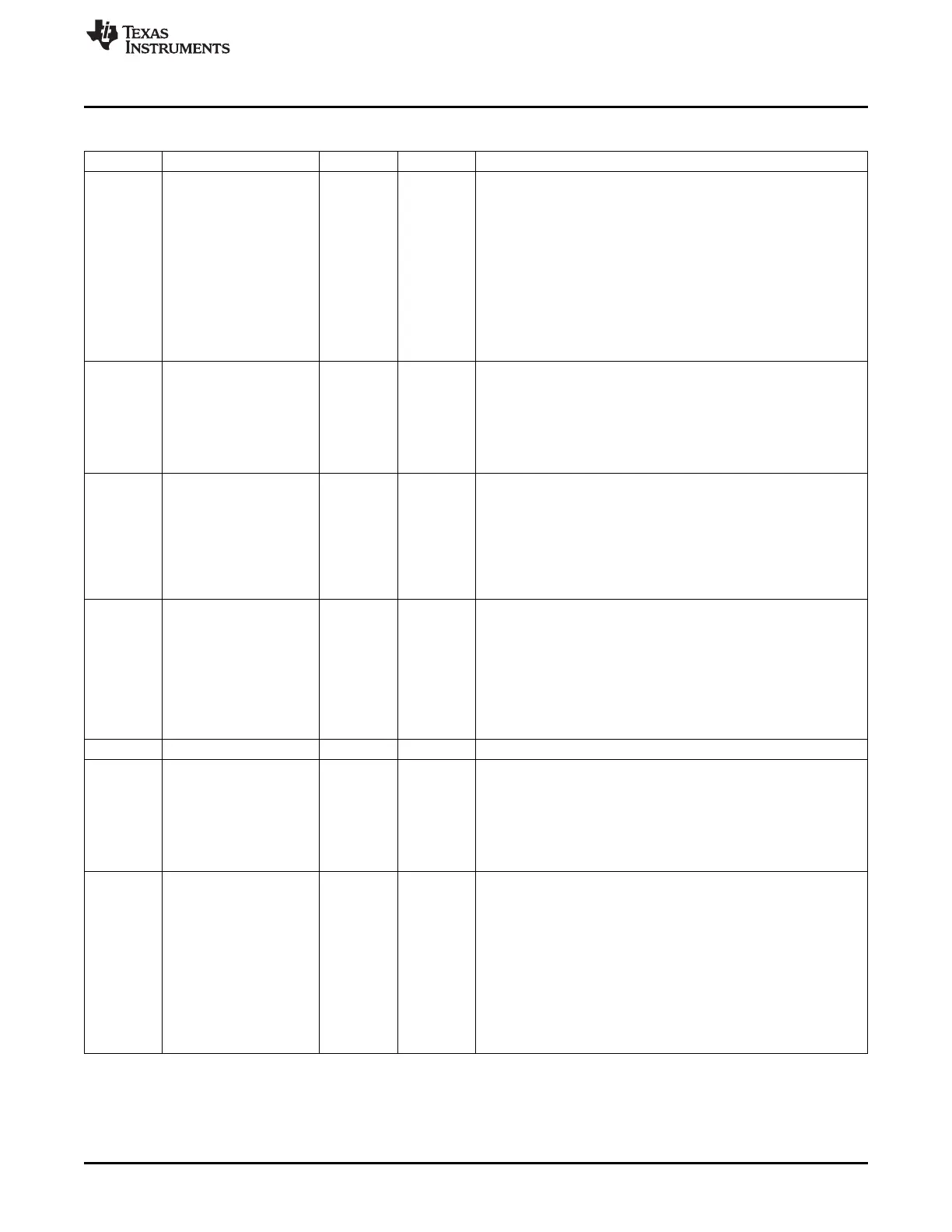

Table 18-24. SD_CON Register Field Descriptions (continued)

Bit Field Type Reset Description

18 BOOT_CF0 R/W 0h Boot Status Supported.

This register is set when the CMD line needs to be forced to 0 for a

boot sequence.

CMD line is driven to 0 after writing in SD_CMD.

The line is released when this bit field is de-asserted and aborts data

transfer in case of a pending transaction.

0x0(W) = CMD line forced to 0 is enabled.

0x0(R) = CMD line not forced.

0x1(W) = CMD line forced to 0 is enabled and will be active after

writing into SD_CMD register.

0x1(R) = CMD line is released when it was previously forced to 0 by

a boot sequence.

17 BOOT_ACK R/W 0h Book acknowledge received.

When this bit is set the controller should receive a boot status on

DAT0 line after next command issued.

If no status is received a data timeout will be generated.

0x0 = No acknowledge to be received.

0x1 = A boot status will be received on DAT0 line after issuing a

command.

16 CLKEXTFREE R/W 0h External clock free running.

This register is used to maintain card clock out of transfer

transaction to enable slave module (for example to generate a

synchronous interrupt on mmc_dat[1] ).

The Clock will be maintain only if SD_SYSCTL[2] CEN bit is set.

0x0 = External card clock is cut off outside active transaction period.

0x1 = External card clock is maintain even out of active transaction

period only if SD_SYSCTL[2] CEN bit is set.

15 PADEN R/W 0h Control power for MMC lines.

This register is only useful when MMC PADs contain power saving

mechanism to minimize its leakage power.

It works as a GPIO that directly control the ACTIVE pin of PADs.

Excepted for mmc_dat[1] , the signal is also combine outside the

module with the dedicated power control SD_CON[11] CTPL bit.

0x0 = ADPIDLE module pin is not forced, it is automatically

generated by the MMC fsms.

0x1 = ADPIDLE module pin is forced to active state

14-13 Reserved R 0h

12 CEATA R/W 0h CE-ATA control mode (MMC cards compliant with CE-ATA).

This bit selects the active level of the out-of-band interrupt coming

from MMC cards.

The usage of the Out-of-Band signal (OBI) is not supported.

0x0 = Standard MMC/SD/SDIO mode.

0x1 = CE-ATA mode. Next commands are considered as CE-ATA

commands.

11 CTPL R/W 0h Control Power for mmc_dat[1] line (SD cards).

By default, this bit is cleared to 0 and the host controller

automatically disables all the input buffers outside of a transaction to

minimize the leakage current.

SDIO cards.

When this bit is set to 1, the host controller automatically disables all

the input buffers except the buffer of mmc_dat[1] outside of a

transaction in order to detect asynchronous card interrupt on

mmc_dat[1] line and minimize the leakage current of the buffers.

0x0 = Disable all the input buffers outside of a transaction.

0x1 = Disable all the input buffers except the buffer of mmc_dat[1]

outside of a transaction.

3399

SPRUH73H–October 2011–Revised April 2013 Multimedia Card (MMC)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...