www.ti.com

Integration

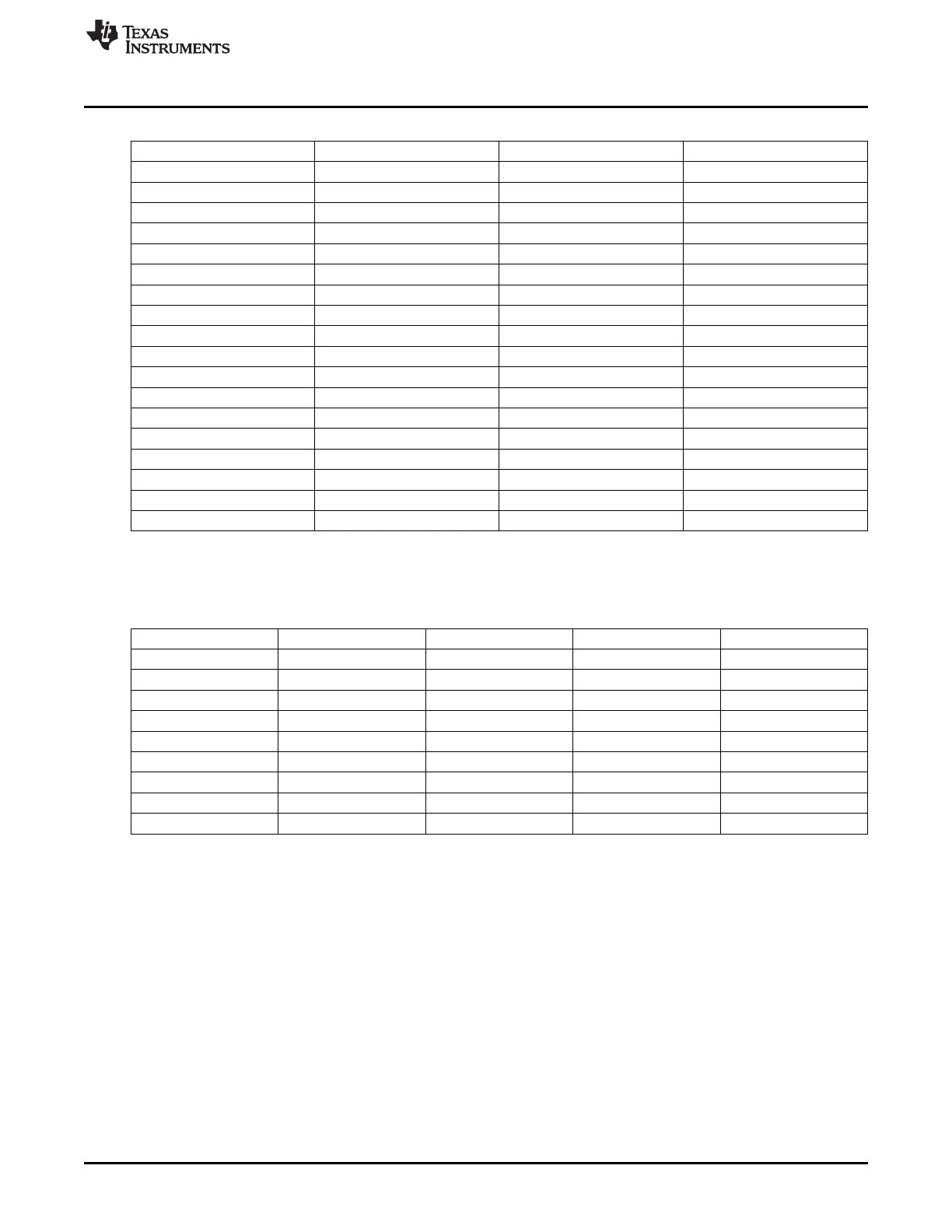

Table 19-6. UART Mode Baud and Error Rates

Baud rate Over sampling Divisor Error (%)

300 16 10000 0

600 16 5000 0

1200 16 2500 0

2400 16 1250 0

4800 16 625 0

9600 16 313 0.16

14400 16 208 0.16

19200 16 156 0.16

28800 16 104 0.16

38400 16 78 0.16

57600 16 52 0.16

115200 16 26 0.16

230400 16 13 0.16

460800 13 8 0.16

921600 13 4 0.16

1843200 13 2 0.16

3000000 16 1 0

3686400 13 1 0.16

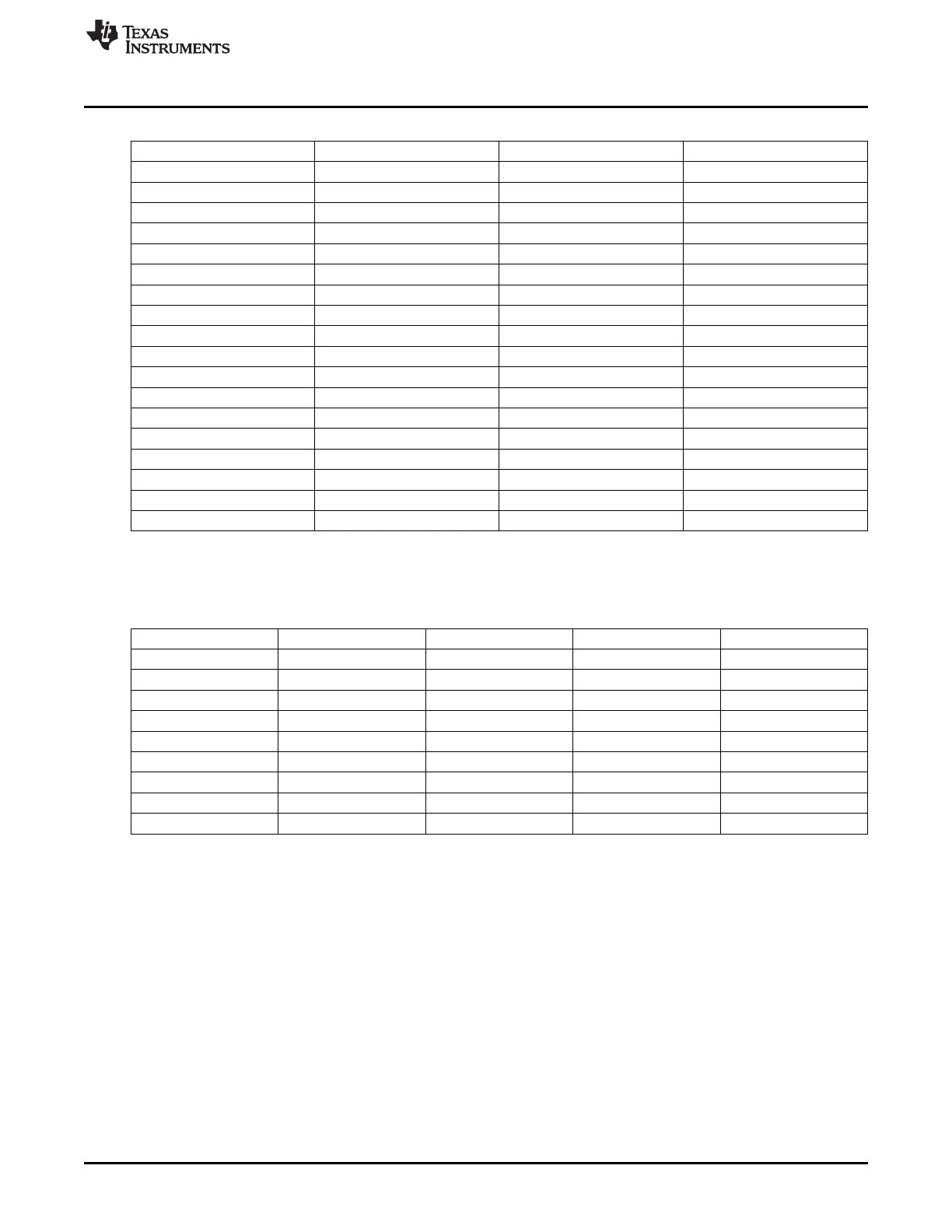

For IrDA operation, the internal functional clock divisor allows generation of SIR, MIR, or FIR baud rates

as shown in Table 19-7.

Table 19-7. IrDA Mode Baud and Error Rates

Baud rate IR mode Encoding Divisor Error (%)

2400 SIR 3/16 1250 0

9600 SIR 3/16 312 0.16

19200 SIR 3/16 156 0.16

38400 SIR 3/16 78 0.16

57600 SIR 3/16 52 0.16

115200 SIR 3/16 26 0.16

576000 MIR 1/4 2 0

1152000 MIR 1/4 1 0

4000000 FIR 4PPM 1 0

3451

SPRUH73H–October 2011–Revised April 2013 Universal Asynchronous Receiver/Transmitter (UART)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...