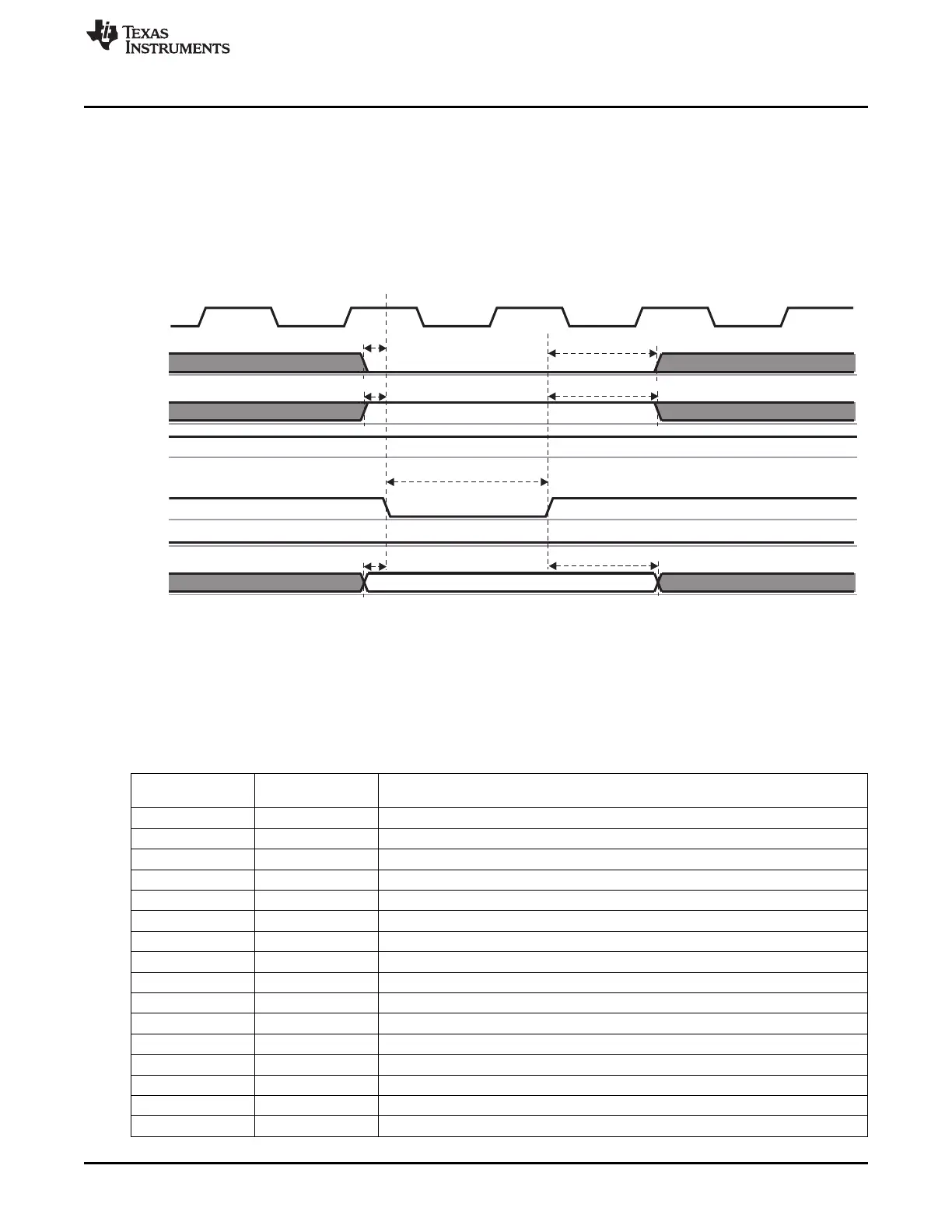

D[15:0]

Command

nBE0/CLE

nCS

nWE

nOE

nADV/ALE

B

G

D

C

F

A

E

www.ti.com

GPMC

K = (OEOffTime - OEOnTime) * (1 + TimeParaGranularity) * GPMC_FCLK period

L = RdCycleTime * (1 + TimeParaGranularity) * GPMC_FCLK period

M = (CSRdOffTime - OEOffTime * (TimeParaGranularity + 1) + 0.5 * (CSExtraDelay - OEExtraDelay ) *

GPMC_FCLK period

Figure 7-44 shows a command latch cycle timing simplified example where formulas are associated with

signal waves.

Figure 7-44. NAND Command Latch Cycle Timing Simplified Example

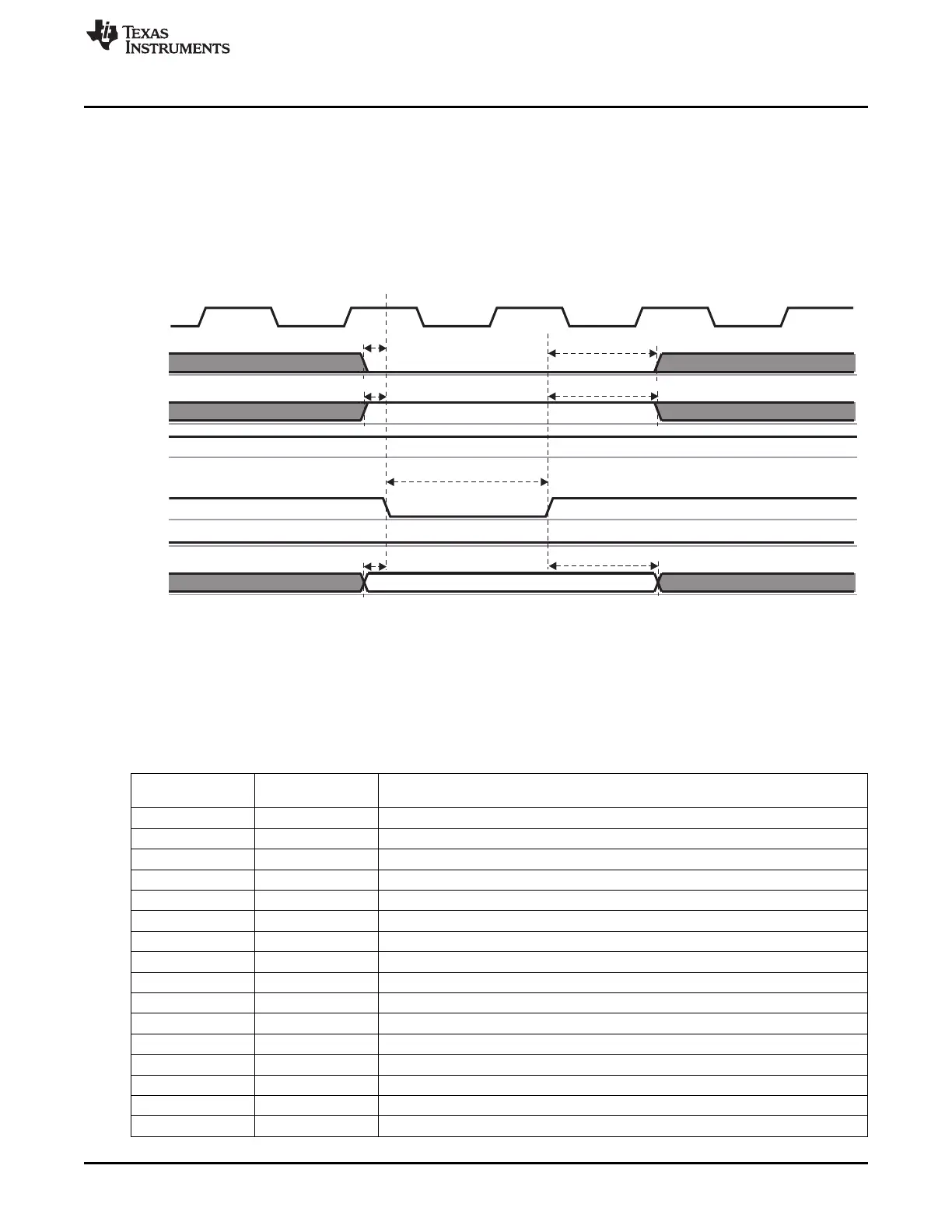

7.1.3.9.1.2 Synchronous NOR Flash Timing Parameters Formulas

This section lists all formulas to use in order to calculate synchronous NOR timing parameters. This is the

case when GPMC_CONFIG1_i[11-10] DEVICETYPE = 0 and when READTYPE or WRITETYPE are set

to synchronous mode.

Table 7-43. Synchronous NOR Formulas Description Table

Configuration

Unit Description

Parameter

A ns Pulse duration - GPMC_CSn low

B ns Delay time - address bus valid to GPMC_CLK first edge

Delay time - GPMC_BE0n_CLE/GPMC_BE1n valid to GPMC_CLK first edge

C ns Pulse duration - GPMC_BE0n_CLE/GPMC_BE1n low

D ns Delay time - GPMC_CLK rising edge to GPMC_BE0n_CLE/GPMC_BE1n invalid

Delay time - GPMC_CLK rising edge to GPMC_ADVn_ALE invalid

E ns Delay time - GPMC_CLK rising edge to GPMC_CSn invalid

Delay time - GPMC_CLK rising edge to GPMC_OEn invalid

F ns Delay time - GPMC_CLK rising edge to GPMC_CSn transition

G ns Delay time - GPMC_CLK rising edge to GPMC_ADVn_ALE transition

H ns Delay time - GPMC_CLK rising edge to GPMC_OEn transition

I ns Delay time - GPMC_CLK rising edge to GPMC_WEn transition

J ns Delay time - GPMC_CLK rising edge to GPMC_AD data bus transition

Delay time - GPMC_CLK rising edge to GPMC_BE0n_CLE/GPMC_BE1n transition

K ns Pulse duration - GPMC_ADVn_ALE low

L ns Delay time - GPMC_WAIT invalid to first data latching GPMC_CLK edge

347

SPRUH73H–October 2011–Revised April 2013 Memory Subsystem

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...