www.ti.com

WATCHDOG

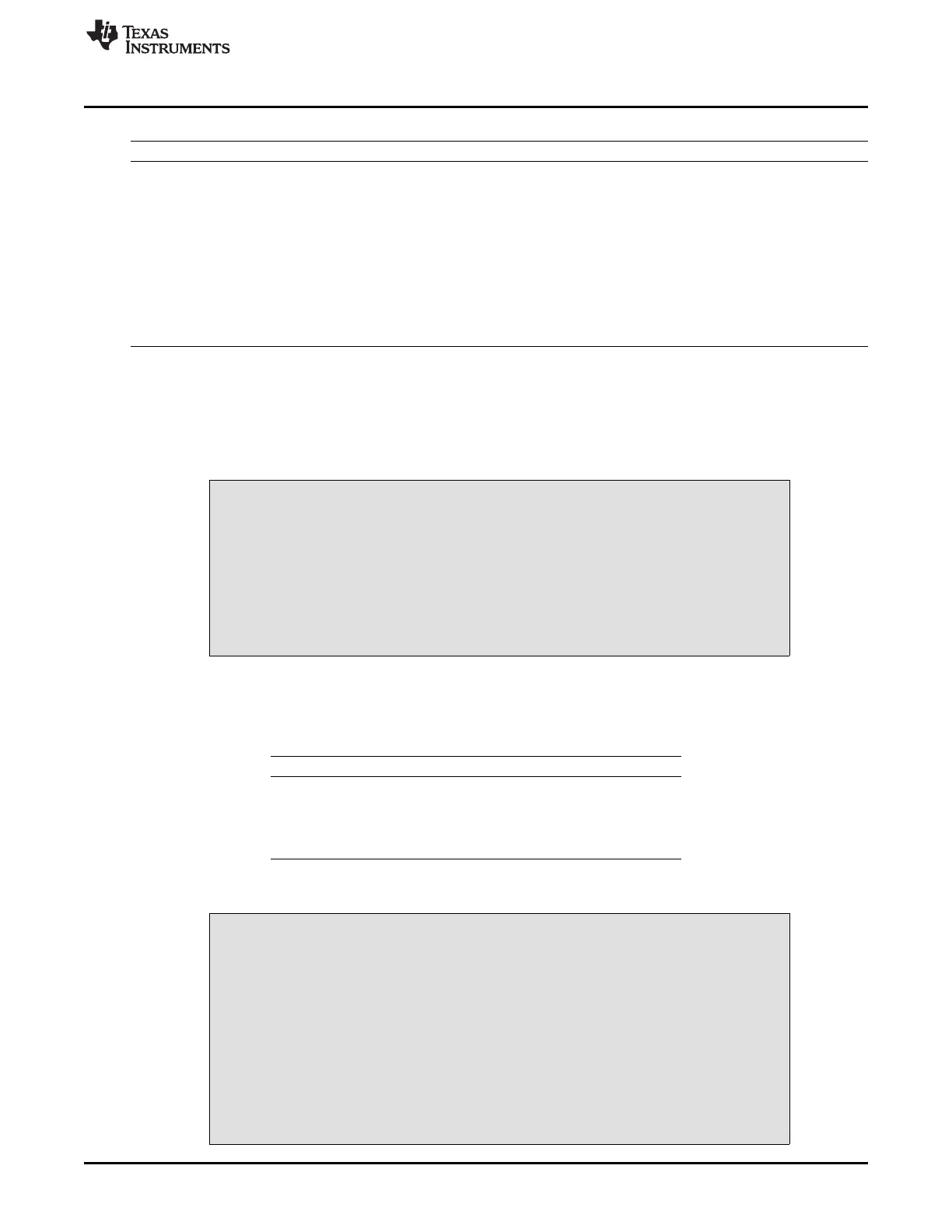

Table 20-103. Prescaler Clock Ratio Values

WDT_WCLR[5] PRE WDT_WCLR[4:2] PTV Clock Divider (PS)

0 X 1

1 0 1

1 1 2

1 2 4

1 3 8

1 4 16

1 5 32

1 6 64

1 7 128

Thus the watchdog timer overflow rate is expressed as:

OVF_Rate = (FFFF FFFFh – WDT_WLDR + 1) × (wd-functional clock period) × PS

where wd-functional clock period = 1/(wd-functional clock frequency) and PS = 2

(PTV)

CAUTION

Internal resynchronization causes some latency in any software write to

WDT_WSPR before WDT_WSPR is updated with the programmed value:

1.5 × functional clock cycles ≤ write_WDT_WSPR_latency ≤ 2.5 × functional

clock cycles

Remember to consider this latency whenever the watchdog timer must be

started or stopped.

For example, for a timer clock input of 32 kHz with a prescaler ratio value of 1 (clock divided by 2) and

WDT_WCLR[5] PRE = 1 (clock divider enabled), the reset period is as listed in Table 20-104.

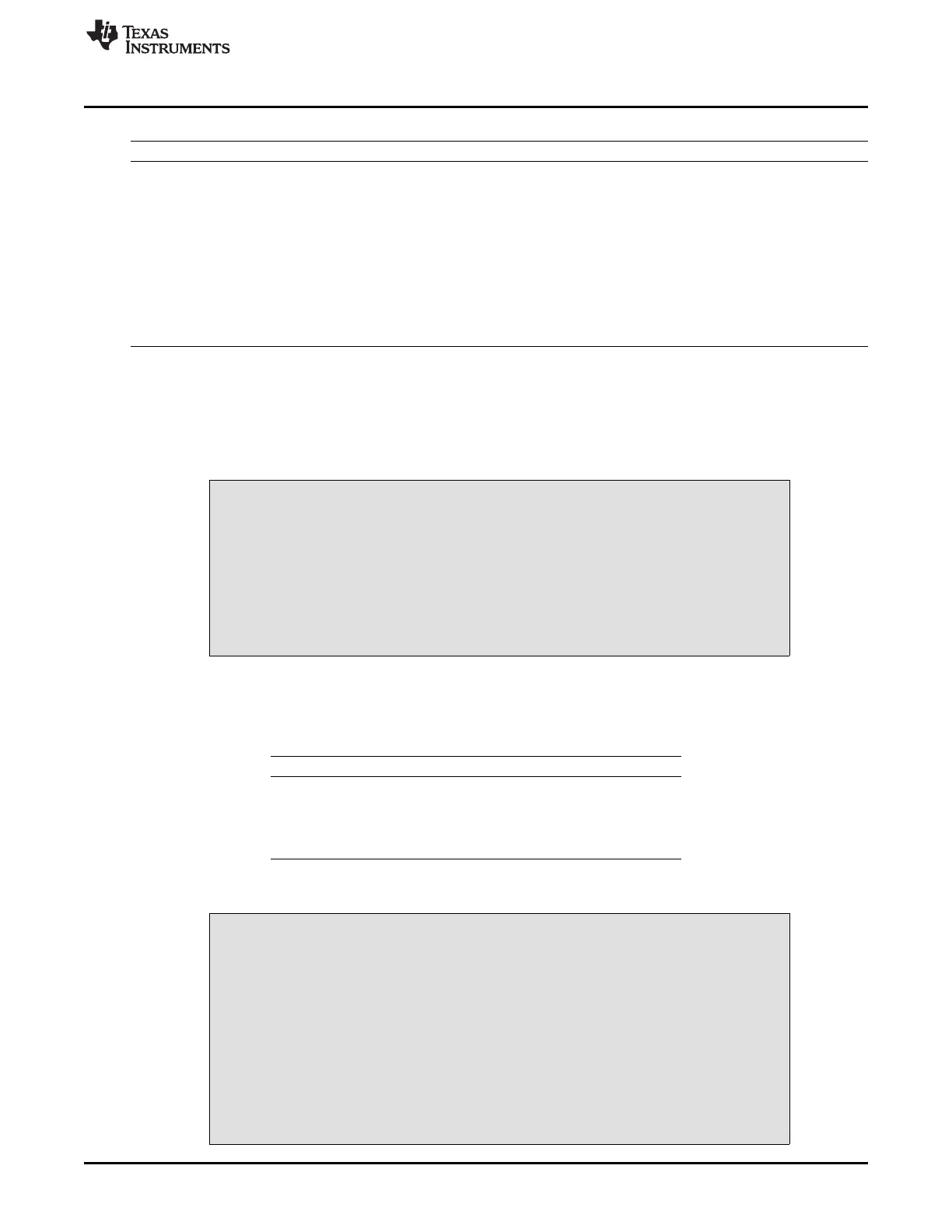

Table 20-104. Reset Period Examples

WDT_WLDR Value Reset Period

0000 0000h 74 h 56 min

FFFF 0000h 4 s

FFFF FFF0h 1 ms

FFFF FFFFh 62.5 us

CAUTION

• Ensure that the reloaded value allows the correct operation of the

application. When a watchdog timer is enabled, software must periodically

trigger a reload before the counter overflows. Hence, the value of the

WDT_WLDR[31:0] bit field must be chosen according to the ongoing activity

preceding the watchdog reload.

• Due to design reasons, WDT_WLDR[31:0] = FFFF FFFFh is a special case,

although such a value of WDT_WLDR is meaningless. When WDT_WLDR

is programmed with the overflow value, a triggering event generates a

reset/interrupt one functional clock cycle later, even if the watchdog timer is

stopped.

3675

SPRUH73H–October 2011–Revised April 2013 Timers

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...