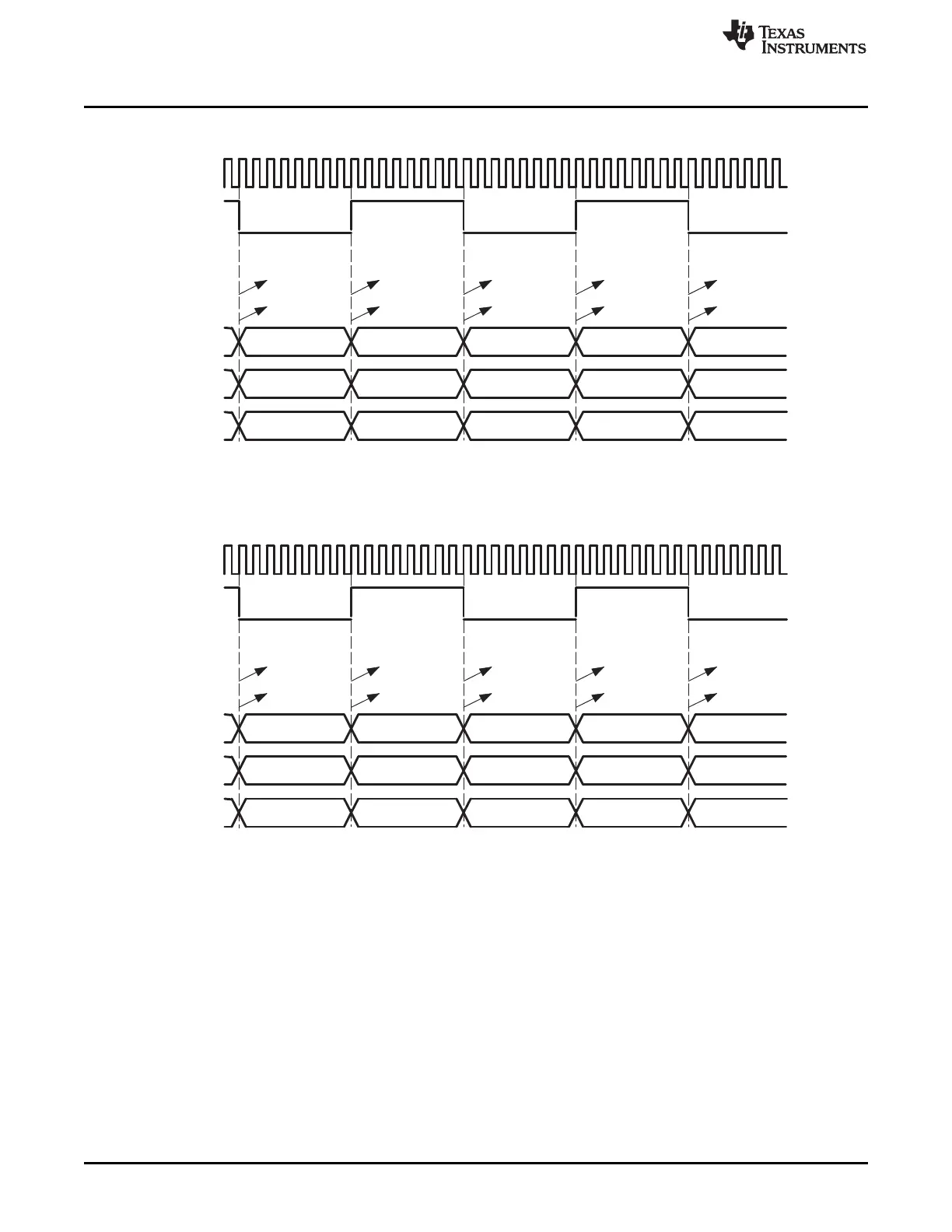

LF1 RF1 LF2 RF2

CLK

FS

AXR4

LS1 RS1 LS2 RS2AXR5

C1 LFE1AXR6 C2 LFE2

AXEVTO

AREVTO

AXEVTE

AREVTE

AXEVTO

AREVTO

AXEVTE

AREVTE

AXEVTO

AREVTO

LF3

LS3

C3

Transmit

Receive

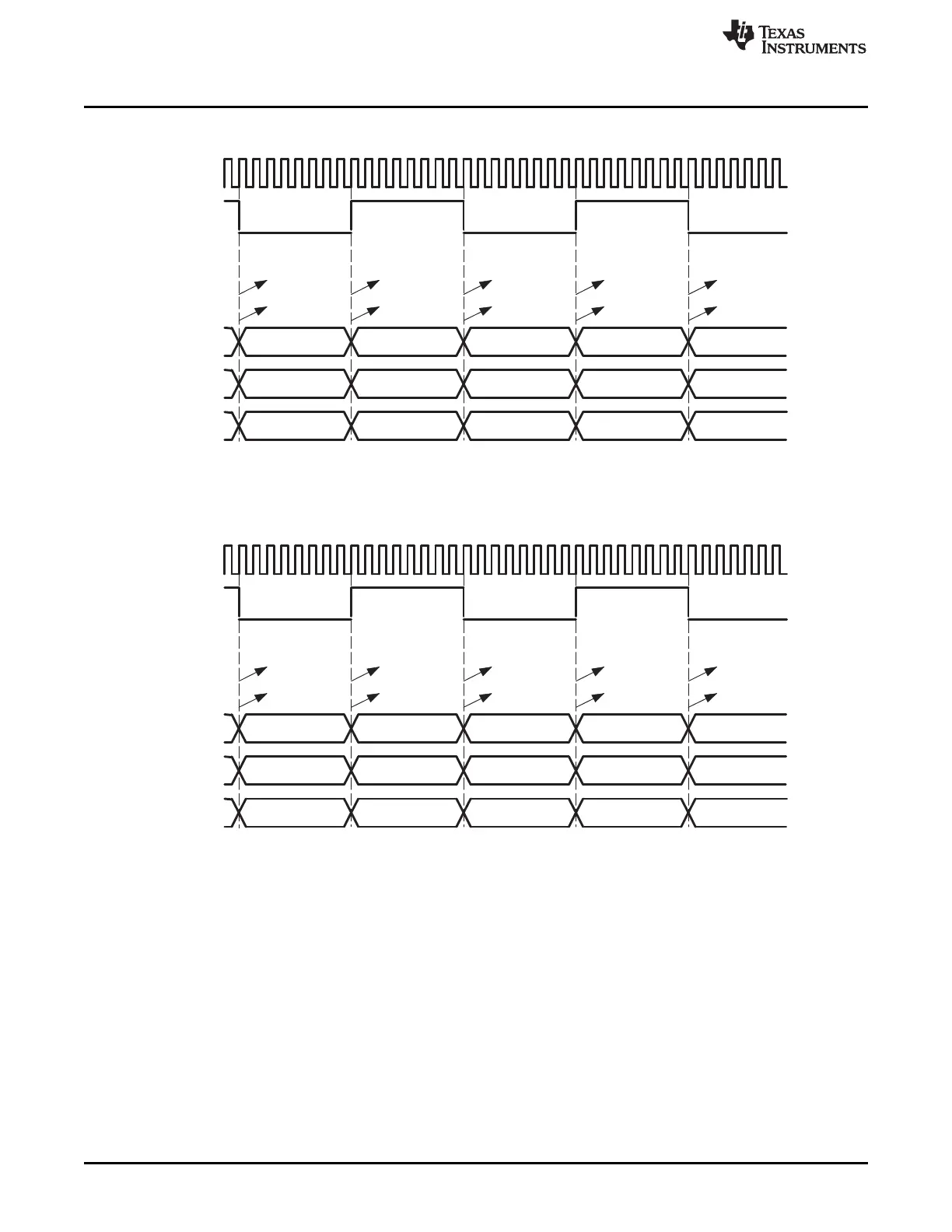

LF1 RF1 LF2 RF2

CLK

FS

AXR4

LS1 RS1 LS2 RS2AXR5

C1 LFE1AXR6 C2 LFE2

AXEVT

AREVT

AXEVT

AREVT

AXEVT

AREVT

AXEVT

AREVT

AXEVT

AREVT

LF3

LS3

C3

Transmit

Receive

Functional Description

www.ti.com

Figure 22-36. DMA Events in an Audio Example–Two Events (Scenario 1)

Figure 22-37. DMA Events in an Audio Example–Four Events (Scenario 2)

In scenario 1 (Figure 22-36), a DMA event AXEVT/AREVT is triggered on each time slot. In the example,

AXEVT is triggered for each of the transmit audio channel time slot (Time slot for channels LF, LS, and C;

and time slot for channels RF, RS, LFE). Similarly, AREVT is triggered for each of the receive audio

channel time slot. Scenario 1 allows for the use of a single DMA to transmit all audio channels, and a

single DMA to receive all audio channels.

In scenario 2 (Figure 22-37), two alternating DMA events are triggered for each time slot. In the example,

AXEVTE (even) is triggered for the time slot for the even audio channels (LF, LS, C) and AXEVTO (odd)

is triggered for the time slot for the odd audio channels (RF, RS, LFE). AXEVTO and AXEVTE alternate in

time. The same is true in the receive direction with the use of AREVTO and AREVTE. This scenario

allows for the use of two DMA channels (odd and even) to transmit all audio channels, and two DMA

channels to receive all audio channels.

3824

Multichannel Audio Serial Port (McASP) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...