McSPI Registers

www.ti.com

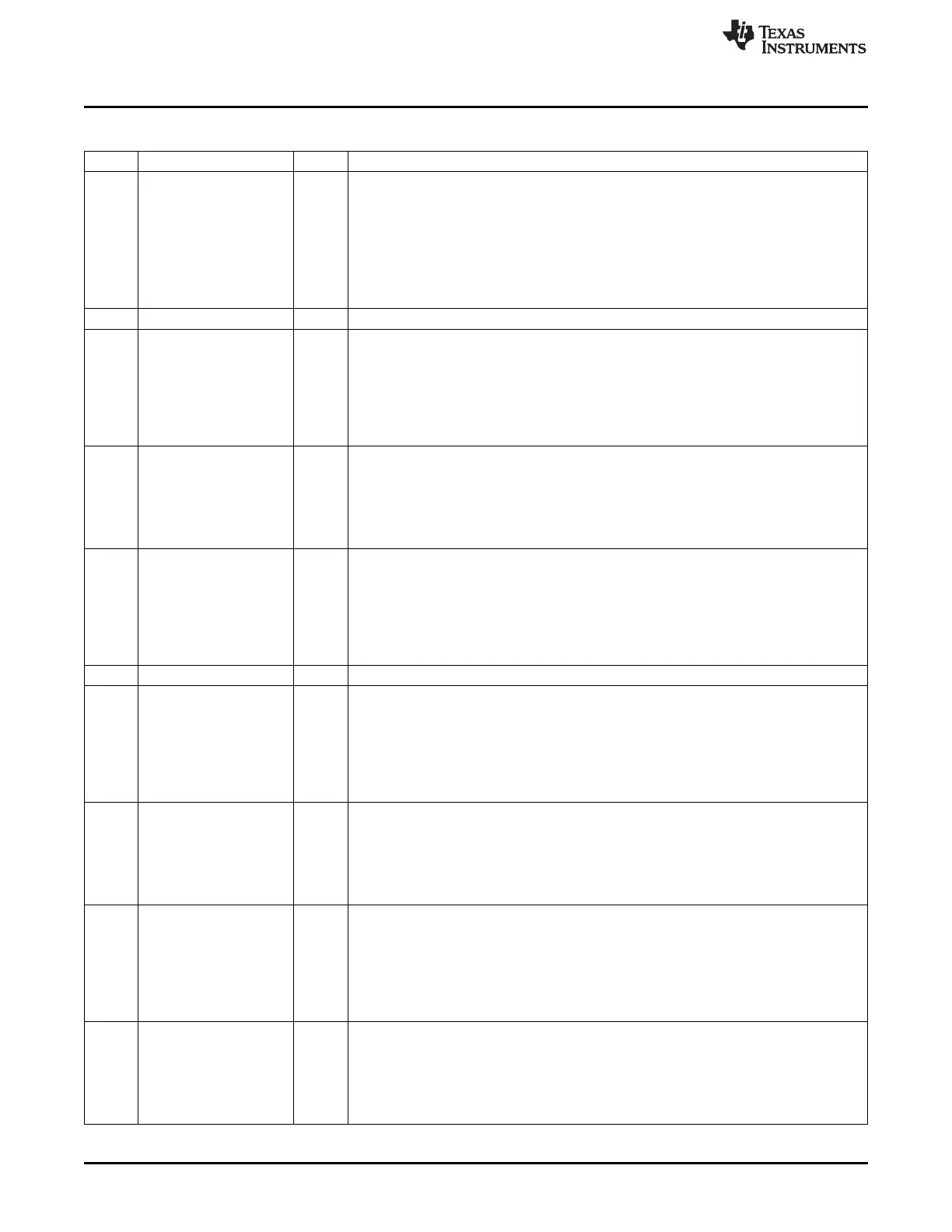

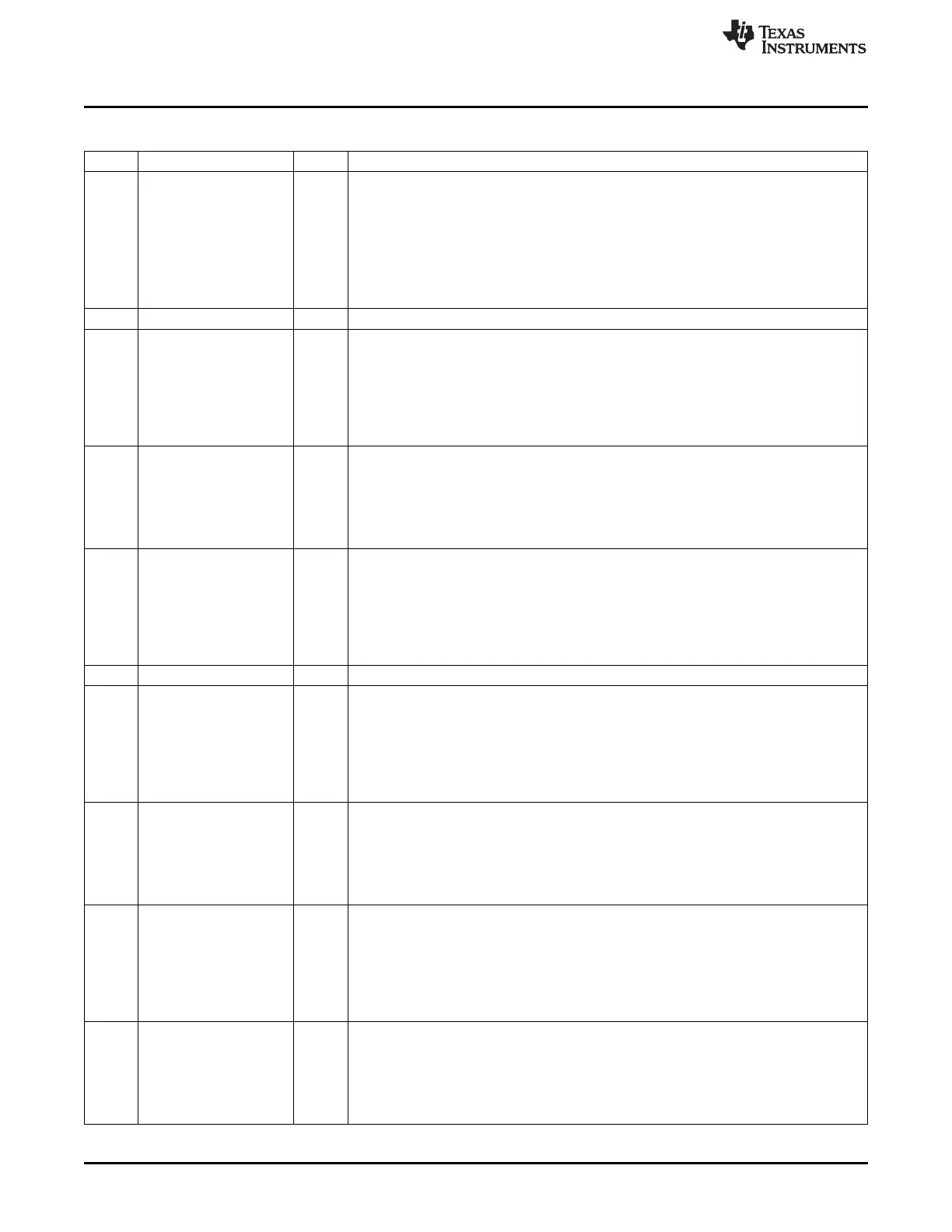

Table 24-14. McSPI Interrupt Status Register (MCSPI_IRQSTATUS) Field Descriptions (continued)

Bit Field Value Description

12 TX3_EMPTY Transmitter register is empty or almost empty. This bit indicate FIFO almost full status when

built-in FIFO is used for transmit register (MCSPI_CH3CONF[FFE3W] is set).

Note: Enabling the channel automatically raises this event.

Write 0 Event status bit is unchanged.

Read 0 Event false.

Write 1 Event status bit is reset.

Read 1 Event is pending.

11 Reserved 0 Reads returns 0

10 RX2_FULL Receiver register full or almost full. Channel 2 This bit indicate FIFO almost full status when

built-in FIFO is used for receive register (MCSPI_CH3CONF[FFE2R] is set).

Write 0 Event status bit is unchanged.

Read 0 Event false.

Write 1 Event status bit is reset.

Read 1 Event is pending.

9 TX2_UNDERFLOW Transmitter register underflow. Channel 2

Write 0 Event status bit is unchanged.

Read 0 Event false.

Write 1 Event status bit is reset.

Read 1 Event is pending.

8 TX2_EMPTY Transmitter register empty or almost empty. Channel 2. This bit indicate FIFO almost full

status when built-in FIFO is used for transmit register (MCSPI_CH3CONF[FFE2W] is set).

Write 0 Event status bit is unchanged.

Read 0 Event false.

Write 1 Event status bit is reset.

Read 1 Event is pending.

7 Reserved 0 Reads returns 0

6 RX1_FULL Receiver register full or almost full. Channel 1. This bit indicate FIFO almost full status when

built-in FIFO is use for receive register (MCSPI_CH3CONF[FFE1R] is set).

Write 0 Event status bit is unchanged.

Read 0 Event false.

Write 1 Event status bit is reset.

Read 1 Event is pending.

5 TX1_UNDERFLOW Transmitter register underflow. Channel 1.

Write 0 Event status bit is unchanged.

Read 0 Event false.

Write 1 Event status bit is reset.

Read 1 Event is pending.

4 TX1_EMPTY Transmitter register empty or almost empty. Channel 1. This bit indicate FIFO almost full

status when built-in FIFO is use for transmit register (MCSPI_CH3CONF[FFE1W] is set).

Write 0 Event status bit is unchanged.

Read 0 Event false.

Write 1 Event status bit is reset.

Read 1 Event is pending.

3 RX0_OVERFLOW Receiver register overflow (slave mode only). Channel 0.

Write 0 Event status bit is unchanged.

Read 0 Event false.

Write 1 Event status bit is reset.

Read 1 Event is pending.

4038

Multichannel Serial Port Interface (McSPI) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...