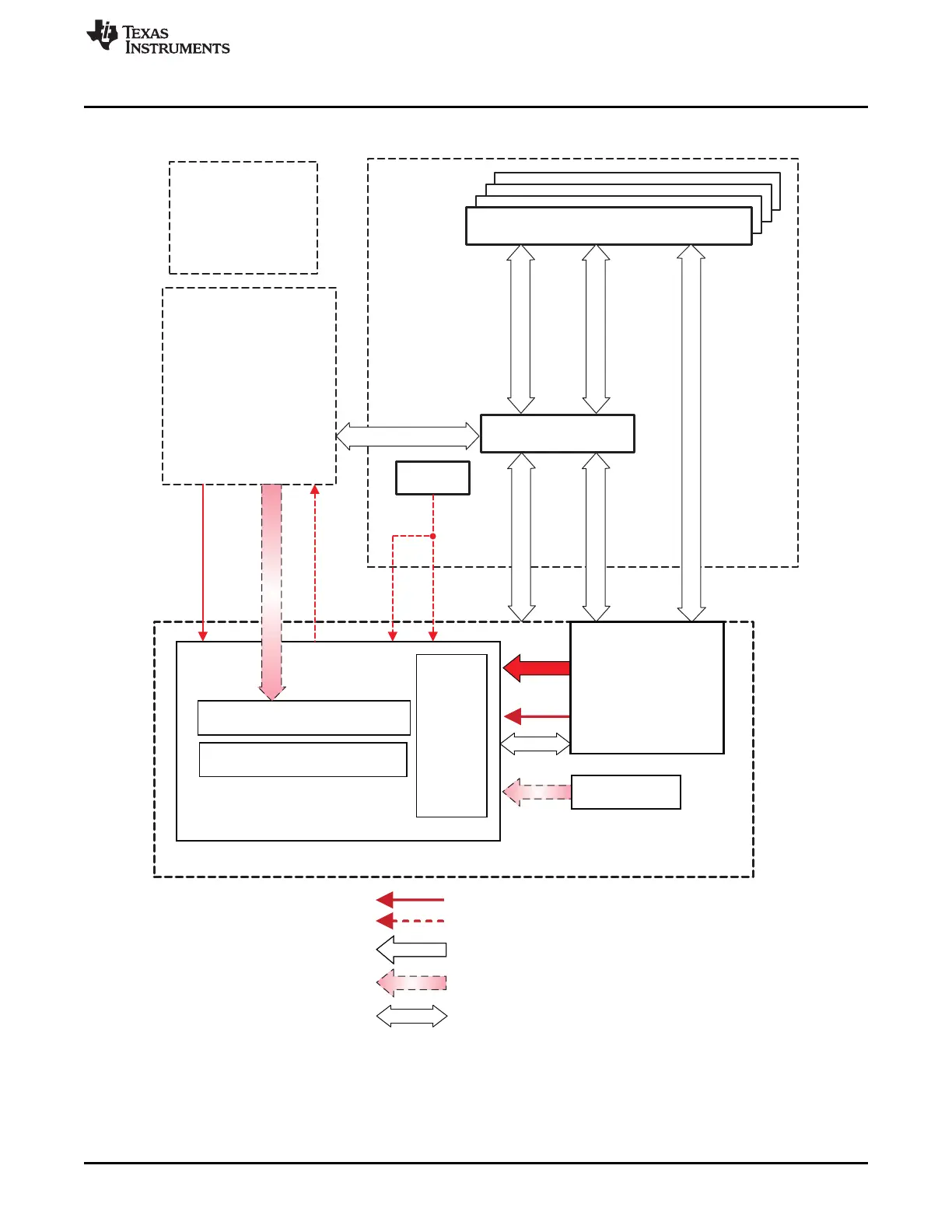

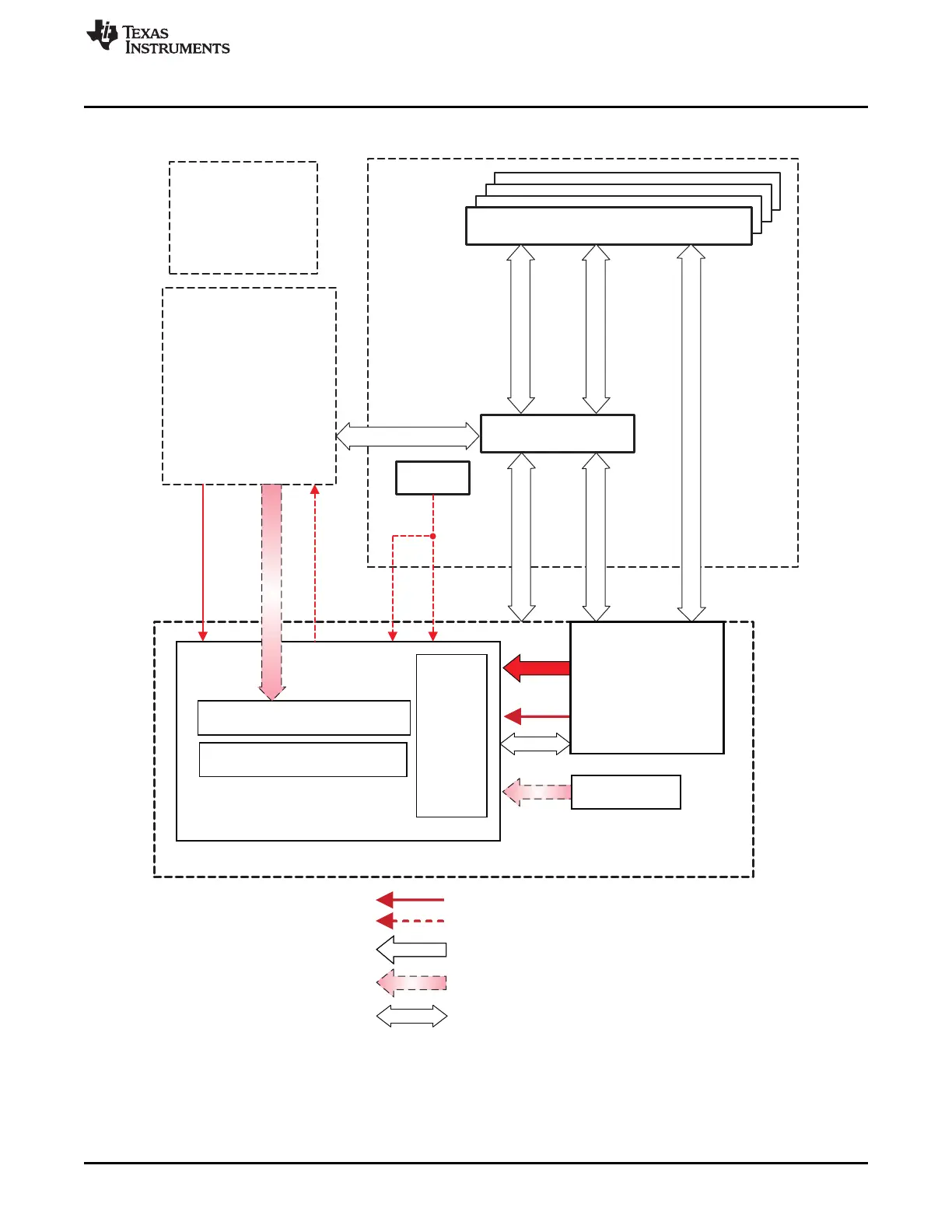

PD_GFX

16KB unified RAM

8KB DRAM

WKUP

System power clock manager

Cortex-M3 subsystem

MSG1

INTR1

Legend:

Interrupt

Alternate Interrupt/Event

s/w message

Alternate s/w message

Data flow

Cortex-

M3

PD_PER

INTR2

MSG3

TXEV

RXEV

INTR3

PD_MPU

(Cortex-A8)

Bus

Power

Idle

Bus

Power

connect/

disconnect

MBX

Interconnect

IP/Peripherals

Power

Idle

MSG3

Control

PRCM

www.ti.com

Power, Reset, and Clock Management

Figure 8-6. System Level View of Power Management of Cortex A8 MPU and Cortex M3

The Cortex-M3 handles all of the low-level power management control of the AM335x. A firmware binary

is provided by Texas Instruments that includes all of the necessary functions to achieve low power modes.

Inter-Processor Communication (IPC) registers (ipc_msg_regx, located in the Control Module Registers)

are available to communicate with the Cortex-M3 so the user can provide certain configuration parameters

based on the level of low power that is required. Figure 8-7 provides a mapping of these registers.

515

SPRUH73H–October 2011–Revised April 2013 Power, Reset, and Clock Management (PRCM)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...