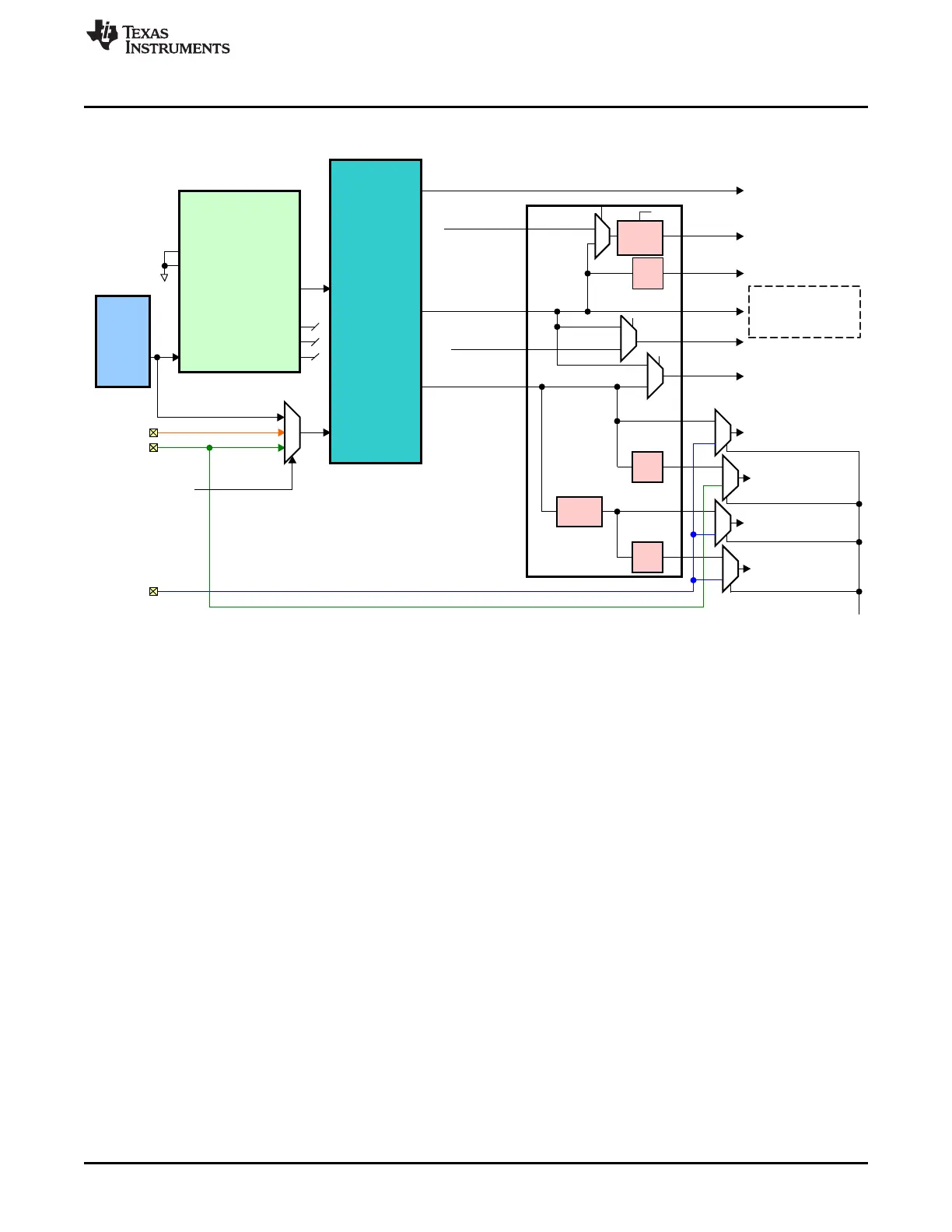

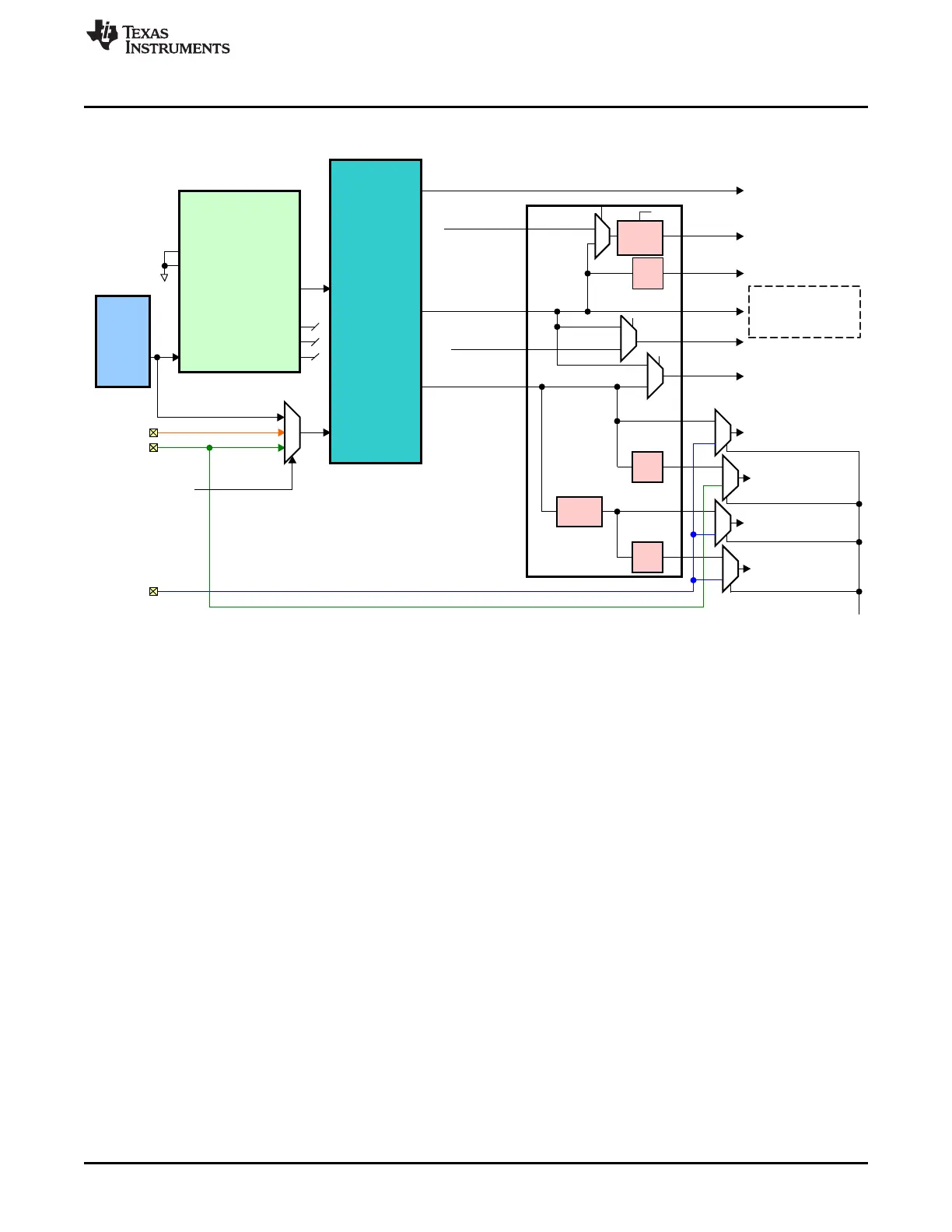

PRCM

Core PLL

(ADPLLS)

CLKDCOLDO

CLKINP

HSDIVIDER

CLKOUT

CLKOUTx2

CLKOUTHIF

CLKINPHIFLDO

M4

M5

SGX CORECLK

M6

CLKINPULOW

ULOWCLKEN

CLKINBYPASS

2

0

1

ALT_CLK3

A

B

0

1

C

0

1

D

0

1

E

Test.CDR (via P1500)

Reset default = 0

/2

/2, /5

/10

/1, /2

(0) (1)

/2

ALT_CLK1

ALT_CLK2

Master

Osc

(CLK_M_OSC)

PER_CLKOUTM2

(192 MHz)

CORE_CLKOUTM4

(200 MHz)

(250 MHz)

CORE_CLKOUTM6

CORE_CLKOUTM5

DISP_CLKOUT

To DDR,

Display, MPU

PLLs

L3F_CLK

L4F_CLK

PRU-ICSS_IEP_CLK,

Debugss_clka

CPTS_RFT_CLK

(Enet switch

IEEE1588v2)

PRU-ICSS OCP_CLKL

L3S_CLK

L4_PER_CLK

L4_WKUP_CLK

MHZ_250_CLK

(RGMII gigabit)

MHZ_125_CLK

(Enet switch bus

interface)

MHZ_50_CLK

(RGMII 100 Mbps

and RMII)

MHZ_5_CLK

(RGMII 10 Mbps)

www.ti.com

Power, Reset, and Clock Management

Figure 8-10. Core PLL

ALT_CLKs are to be used for internal test purpose and should not be used in functional mode.

525

SPRUH73H–October 2011–Revised April 2013 Power, Reset, and Clock Management (PRCM)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...