Functional Description

www.ti.com

Note that PaRAM updates only pertain to the information that is needed to properly submit the next

transfer request to the EDMA3TC. Updates that occur while data is moved within a transfer request are

tracked within the transfer controller, and is detailed in Section 11.3.12. For A-synchronized transfers, the

EDMA3CC always submits a TRP for ACNT bytes (BCNT = 1 and CCNT = 1). For AB-synchronized

transfers, the EDMA3CC always submits a TRP for ACNT bytes of BCNT arrays (CCNT = 1). The

EDMA3TC is responsible for updating source and destination addresses within the array based on ACNT

and FWID (in OPT). For AB-synchronized transfers, the EDMA3TC is also responsible to update source

and destination addresses between arrays based on SRCBIDX and DSTBIDX.

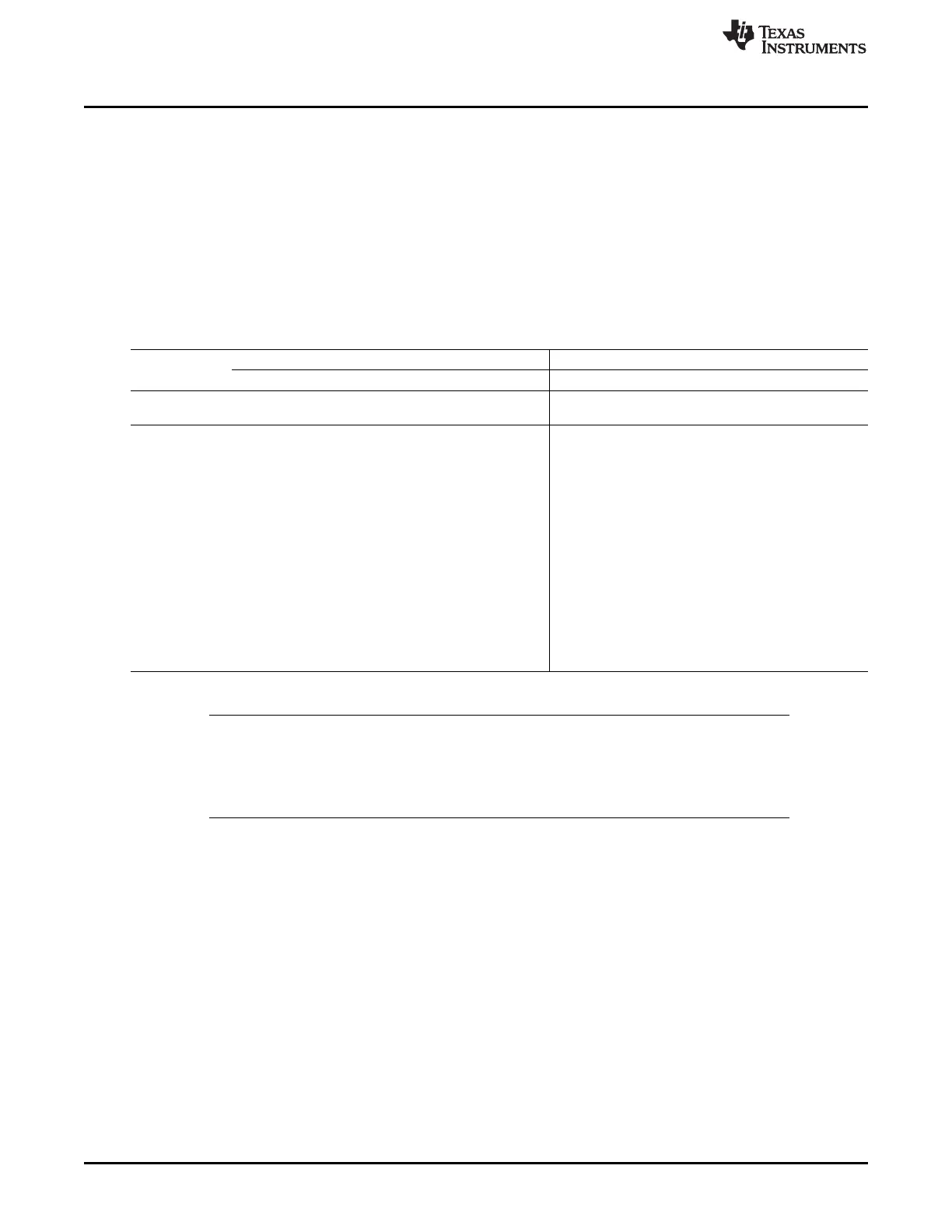

Table 11-9 shows the details of parameter updates that occur within EDMA3CC for A-synchronized and

AB-synchronized transfers.

Table 11-9. Parameter Updates in EDMA3CC (for Non-Null, Non-Dummy PaRAM Set)

A-Synchronized Transfer AB-Synchronized Transfer

B-Update C-Update Link Update B-Update C-Update Link Update

BCNT == 1 && BCNT == 1 &&

Condition: BCNT > 1 CCNT > 1 CCNT == 1 N/A CCNT > 1 CCNT == 1

SRC += SRCBIDX += SRCCIDX = Link.SRC in EDMA3TC += SRCCIDX = Link.SRC

DST += DSTBIDX += DSTCIDX = Link.DST in EDMA3TC += DSTCIDX = Link.DST

ACNT None None = Link.ACNT None None = Link.ACNT

BCNT –= 1 = BCNTRLD = Link.BCNT in EDMA3TC N/A = Link.BCNT

CCNT None –= 1 = Link.CCNT in EDMA3TC –=1 = Link.CCNT

SRCBIDX None None = Link.SRCBIDX in EDMA3TC None = Link.SRCBIDX

DSTBIDX None None = Link.DSTBIDX None None = Link.DSTBIDX

SRCCIDX None None = Link.SRCBIDX in EDMA3TC None = Link.SRCBIDX

DSTCIDX None None = Link.DSTBIDX None None = Link.DSTBIDX

LINK None None = Link.LINK None None = Link.LINK

BCNTRLD None None = Link.BCNTRLD None None = Link.BCNTRLD

OPT

(1)

None None = LINK.OPT None None = LINK.OPT

(1)

In all cases, no updates occur if OPT.STATIC == 1 for the current PaRAM set.

NOTE: The EDMA3CC includes no special hardware to detect when an indexed address update

calculation overflows/underflows. The address update will wrap across boundaries as

programmed by the user. You should ensure that no transfer is allowed to cross internal port

boundaries between peripherals. A single TR must target a single source/destination slave

endpoint.

890

Enhanced Direct Memory Access (EDMA) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...