Base

BGR

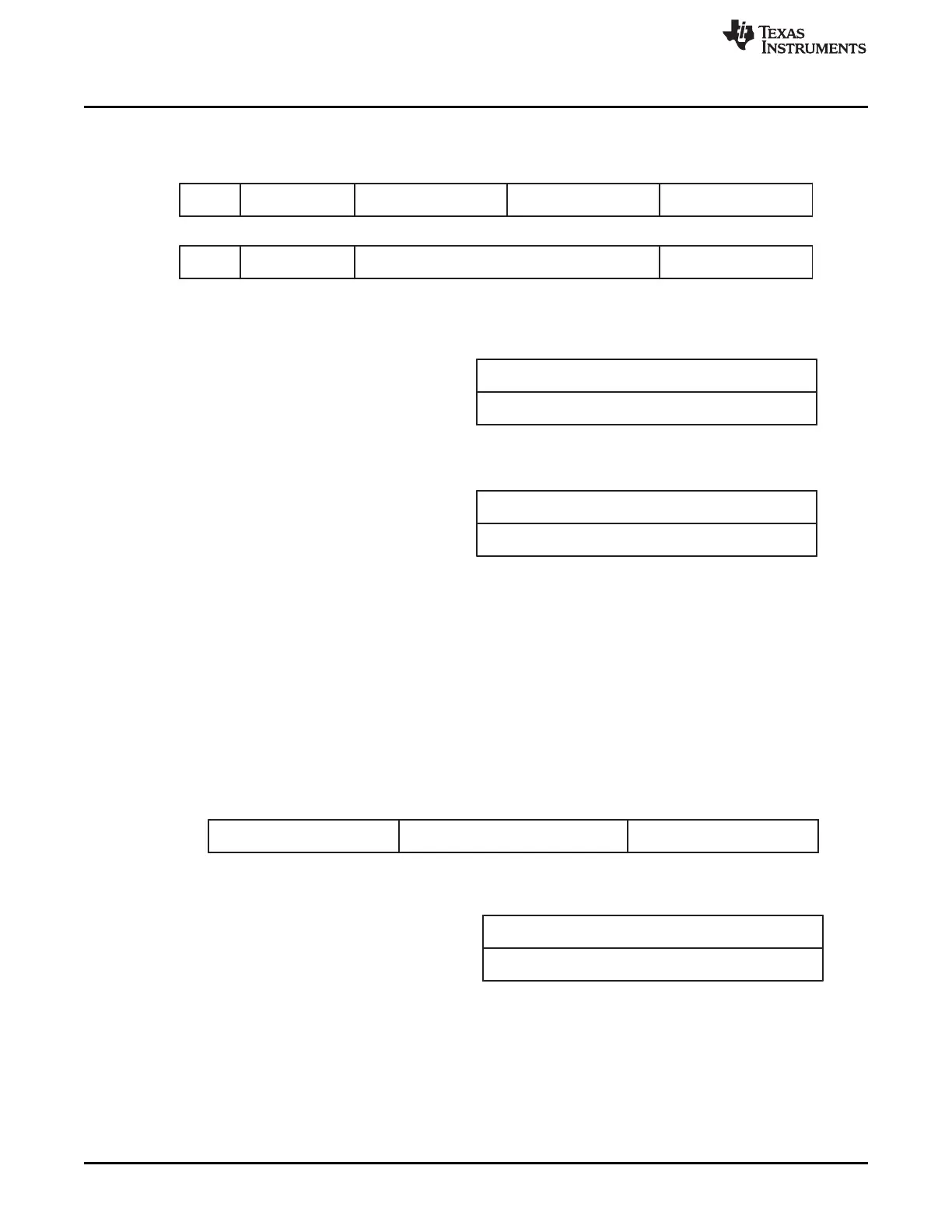

15 01234567891011121314

16 bits/pixel

Bit

Pixel 0

Pixel 1

Bit

15

0

Base + 2

Base + 0

Individual Palette Entry

Unused Blue (B)Green (G)Red (R)BPP

(A)

15 01234567891011121314

Mono (M)Unused

A. Bits-per-pixels (BPP) is only contained within the first palette entry (palette entry 0).

Color

Bit

Bit

Mono

15 01234567891011121314

256-Entry Palette Buffer

Palette Entry 0

Palette Entry 1

Palette Entry 254

Palette Entry 255

Bit

15

0

Base + 2

Base + FCh

Base + FEh

Unused BPP

(A)

.

.

.

.

.

.

Functional Description

www.ti.com

Figure 13-7. 256-Entry Palette/Buffer Format (8 BPP)

Bits 12, 13, and 14 of the first palette entry select the number of bits-per-pixel to be used in the following

frame and thus the number of palette RAM entries. The palette entry is used by the Raster Controller to

correctly unpack pixel data.

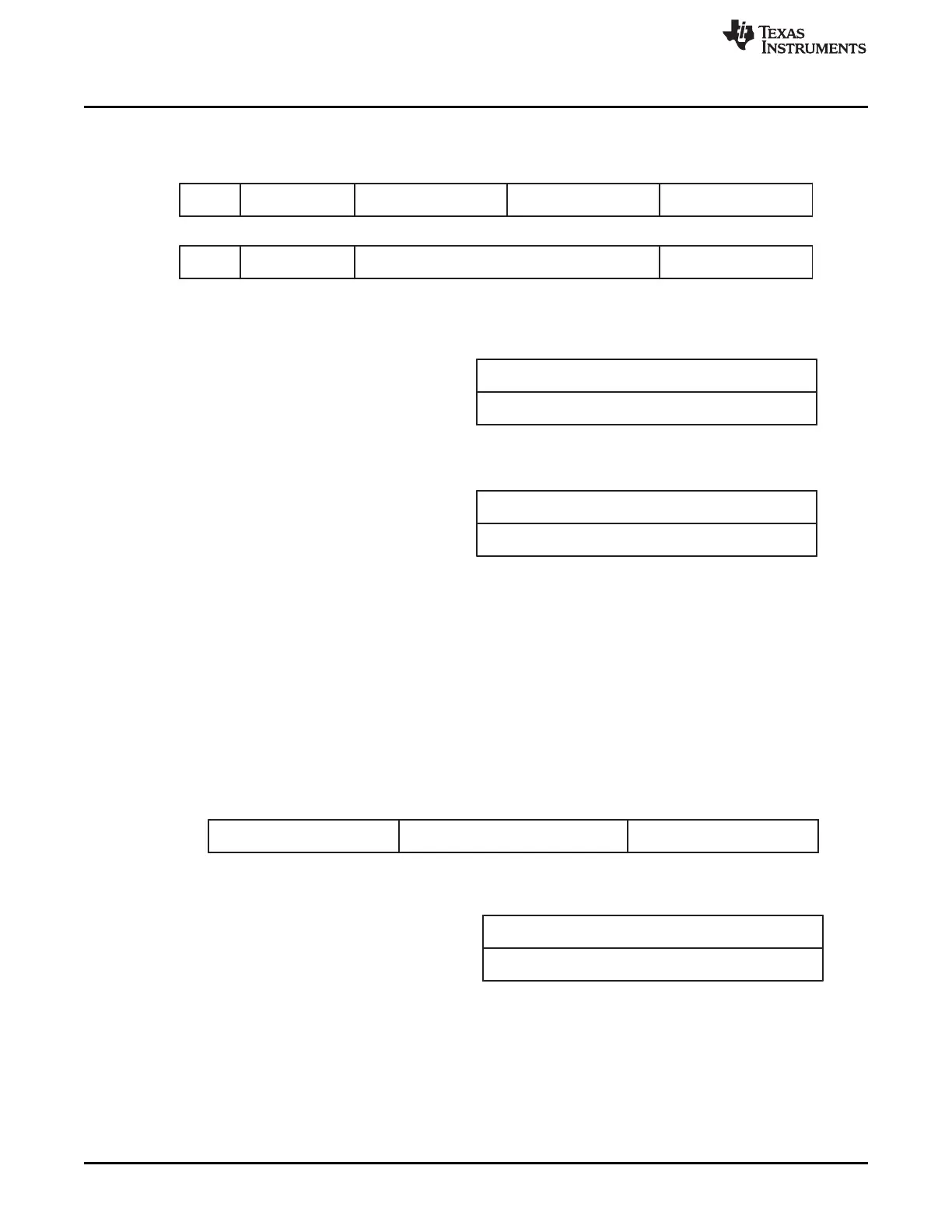

Figure 13-8 through Figure 13-13 show the memory organization within the frame buffer for each pixel

encoding size.

Figure 13-8. 16-BPP Data Memory Organization (TFT Mode Only)—Little Endian

1112

LCD Controller SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...