ARM Cortex-A8 Memory Map

www.ti.com

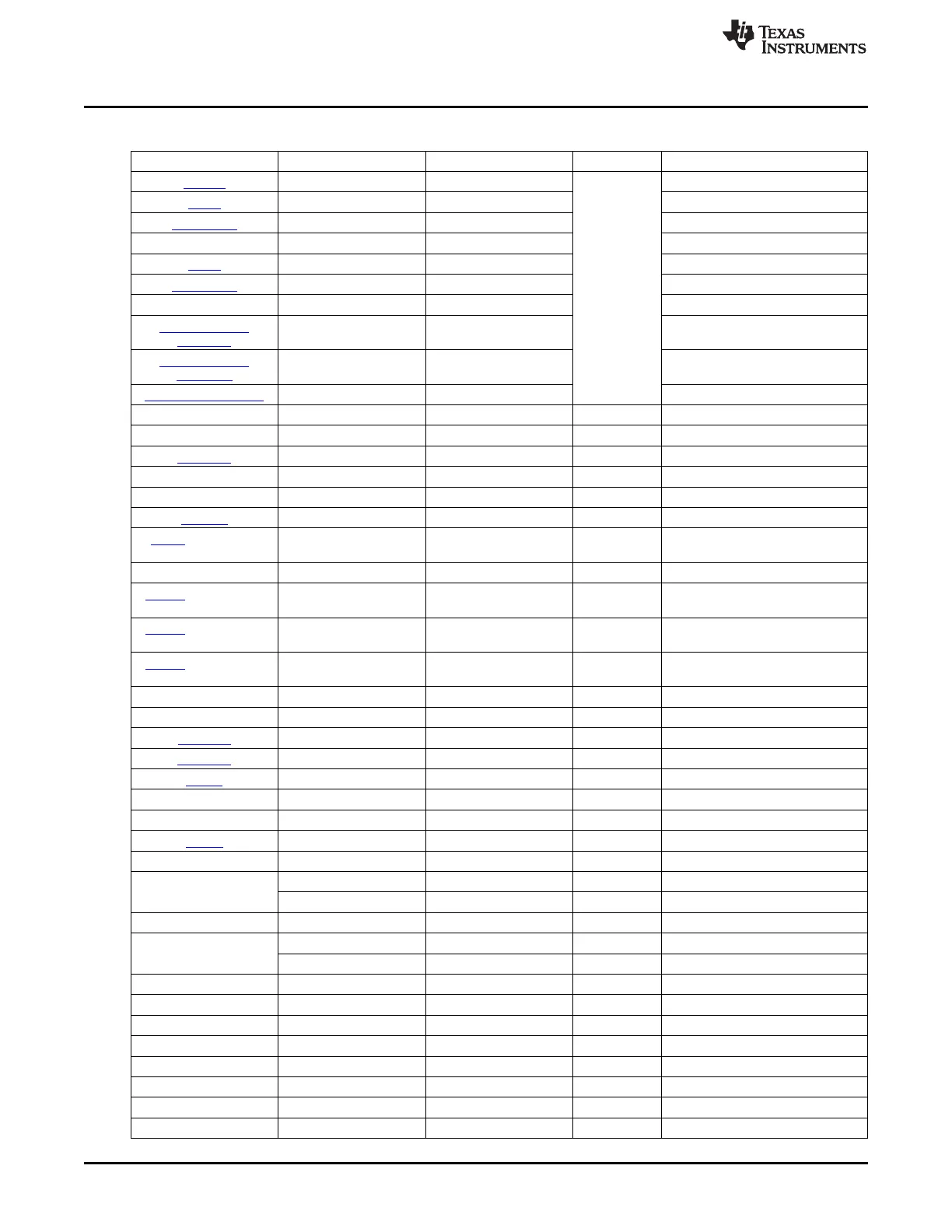

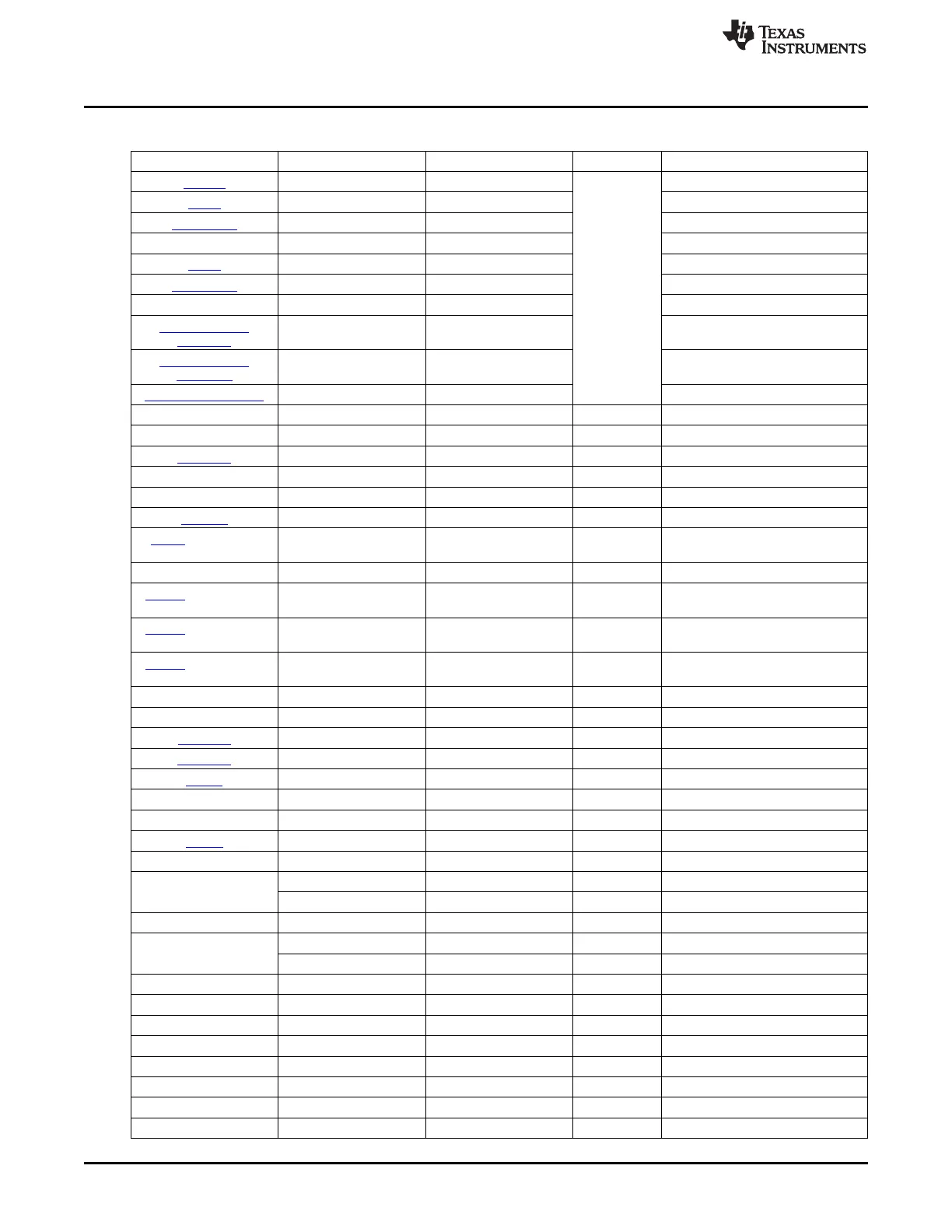

Table 2-1. L3 Memory Map (continued)

Block Name Start_address (hex) End_address (hex) Size Description

USBSS 0x4740_0000 0x4740_0FFF 20KB USB Subsystem Registers

USB0 0x4740_1000 0x4740_12FF USB0 Controller Registers

USB0_PHY 0x4740_1300 0x4740_13FF USB0 PHY Registers

USB0 Core 0x4740_1400 0x4740_17FF USB0 Core Registers

USB1 0x4740_1800 0x4740_1AFF USB1 Controller Registers

USB1_PHY 0x4740_1B00 0x4740_1BFF USB1 PHY Registers

USB1 Core 0x4740_1C00 0x4740_1FFF USB1 Core Registers

USB CPPI DMA 0x4740_2000 0x4740_2FFF USB CPPI DMA Controller

Controller Registers

USB CPPI DMA 0x4740_3000 0x4740_3FFF USB CPPI DMA Scheduler

Scheduler Registers

USB Queue Manager 0x4740_4000 0x4740_4FFF USB Queue Manager Registers

Reserved 0x4740_5000 0x477F_FFFF 4MB-20KB Reserved

Reserved 0x4780_0000 0x4780_FFFF 64KB Reserved

MMCHS2 0x4781_0000 0x4781_FFFF 64KB MMCHS2

Reserved 0x4782_0000 0x47BF_FFFF 4MB-128KB Reserved

Reserved 0x47C0_0000 0x47FF_FFFF 4MB Reserved

L4_PER 0x4800_0000 0x48FF_FFFF 16MB L4 Peripheral (see L4_PER table)

TPCC (EDMA3CC) 0x4900_0000 0x490F_FFFF 1MB EDMA3 Channel Controller

Registers

Reserved 0x4910_0000 0x497F_FFFF 7MB Reserved

TPTC0 (EDMA3TC0) 0x4980_0000 0x498F_FFFF 1MB EDMA3 Transfer Controller 0

Registers

TPTC1 (EDMA3TC1) 0x4990_0000 0x499F_FFFF 1MB EDMA3 Transfer Controller 1

Registers

TPTC2 (EDMA3TC2) 0x49A0_0000 0x49AF_FFFF 1MB EDMA3 Transfer Controller 2

Registers

Reserved 0x49B0_0000 0x49BF_FFFF 1MB Reserved

Reserved 0x49C0_0000 0x49FF_FFFF 4MB Reserved

L4_FAST 0x4A00_0000 0x4AFF_FFFF 16MB L4_FAST

DebugSS 0x4B00_0000 0x4BFF_FFFF 16MB Debug Subsystem region

EMIF0 0x4C00_0000 0x4CFF_FFFF 16MB EMIF0 Configuration registers

Reserved 0x4D00_0000 0x4DFF_FFFF 16MB Reserved

Reserved 0x4E00_0000 0x4FFF_FFFF 32MB Reserved

GPMC 0x5000_0000 0x50FF_FFFF 16MB GPMC Configuration registers

Reserved 0x5100_0000 0x52FF_FFFF 32MB Reserved

Reserved 0x5300_0000 0x530F_FFFF 1MB Reserved

0x5310_0000 0x531F_FFFF 1MB Reserved

Reserved 0x5320_0000 0x533F_FFFF 2MB Reserved

Reserved 0x5340_0000 0x534F_FFFF 1MB Reserved

0x5350_0000 0x535F_FFFF 1MB Reserved

Reserved 0x5360_0000 0x54BF_FFFF 22MB Reserved

ADC_TSC DMA 0x54C0_0000 0x54FF_FFFF 4MB ADC_TSC DMA Port

Reserved 0x5500_0000 0x55FF_FFFF 16MB Reserved

SGX530 0x5600_0000 0x56FF_FFFF 16MB SGX530 Slave Port

Reserved 0x5700_0000 0x57FF_FFFF 16MB Reserved

Reserved 0x5800_0000 0x58FF_FFFF 16MB Reserved

Reserved 0x5900_0000 0x59FF_FFFF 16MB Reserved

Reserved 0x5A00_0000 0x5AFF_FFFF 16MB Reserved

156

Memory Map SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...